## S1D13704 Embedded Memory Color LCD Controller

# S1D13704 TECHNICAL MANUAL

Issue Date: 01/02/12

Document Number: X26A-Q-001-04

Copyright © 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

THIS PAGE LEFT BLANK

# **Customer Support Information**

### **Comprehensive Support Tools**

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a complete set of resources and tools for the development of graphics systems.

### **Evaluation / Demonstration Board**

- Assembled and fully tested graphics evaluation board with installation guide and schematics.

- To borrow an evaluation board, please contact your local Seiko Epson Corp. sales representative.

### **Chip Documentation**

Technical manual includes Data Sheet, Application Notes, and Programmer's Reference.

### **Software**

- OEM Utilities.

- User Utilities.

- Evaluation Software.

- To obtain these programs, contact Application Engineering Support.

### **Application Engineering Support**

Engineering and Sales Support is provided by:

#### Japan

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

#### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

#### **North America**

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

#### Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110 Taiwan, R.O.C.

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan, R.O.C. Tel: 02-2717-7360

Fax: 02-2717-7360

#### Singapore

Fax: 334-2716

Epson Singapore Pte., Ltd. No. 1 Temasek Avenue #36-00 Millenia Tower Singapore, 039192 Tel: 337-7911

TECHNICAL MANUAL Issue Date: 01/02/12 THIS PAGE LEFT BLANK

### **Table of Contents**

### INTRODUCTION

S1D13704 Embedded Memory Color LCD Controller Product Brief

#### **SPECIFICATION**

S1D13704 Hardware Functional Specification

#### PROGRAMMER'S REFERENCE

S1D13704 Programming Notes and Examples S1D13704 Register Summary

#### **UTILITIES**

13704CFG.EXE File Configuration Program

13704SHOW Demonstration Program

13704SPLT Display Utility

13704VIRT Display Utility

13704PLAY Diagnostic Utility

13704BMP Demonstration Program

13704PWR Power Save Utility

### **DRIVERS**

S1D13704 Windows® CE Display Drivers

#### **EVALUATION**

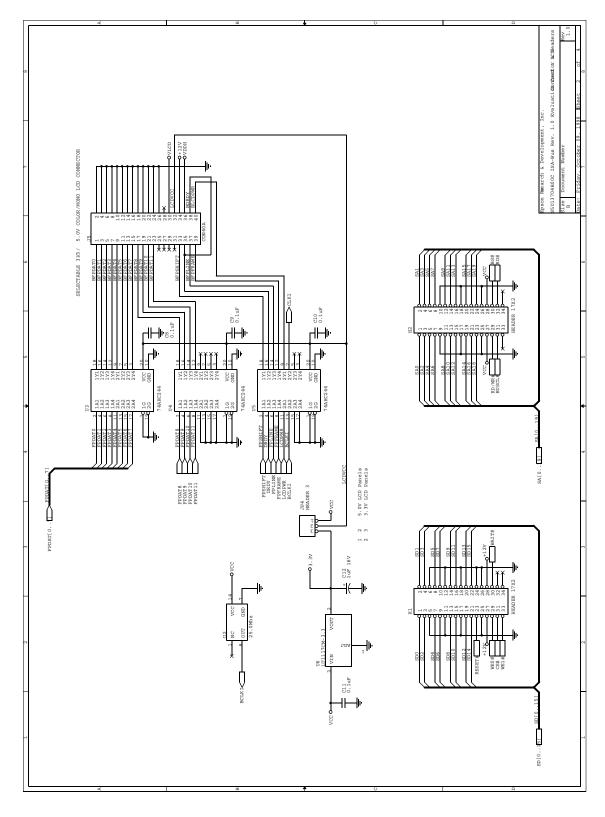

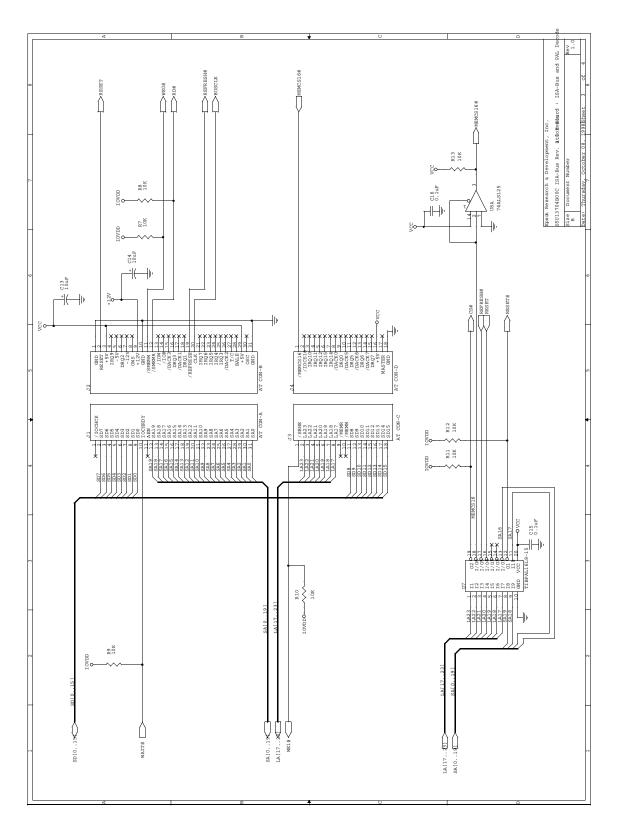

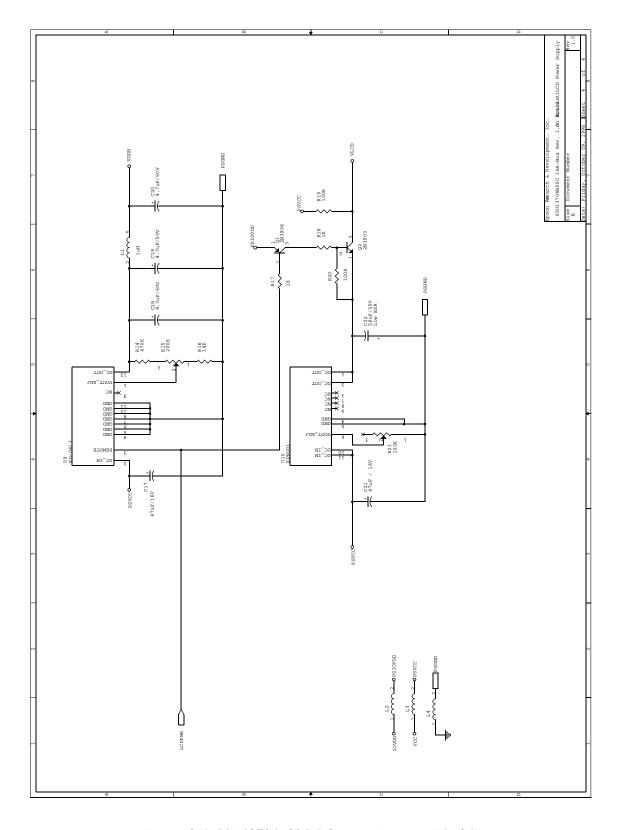

S5U13704B00C Rev. 1 ISA Bus Evaluation Board User Manual

### **APPLICATION NOTES**

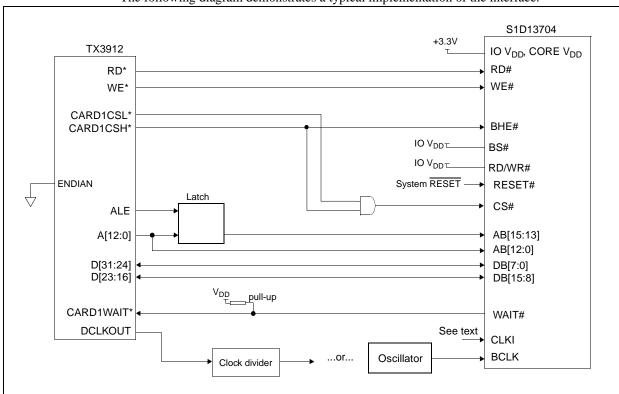

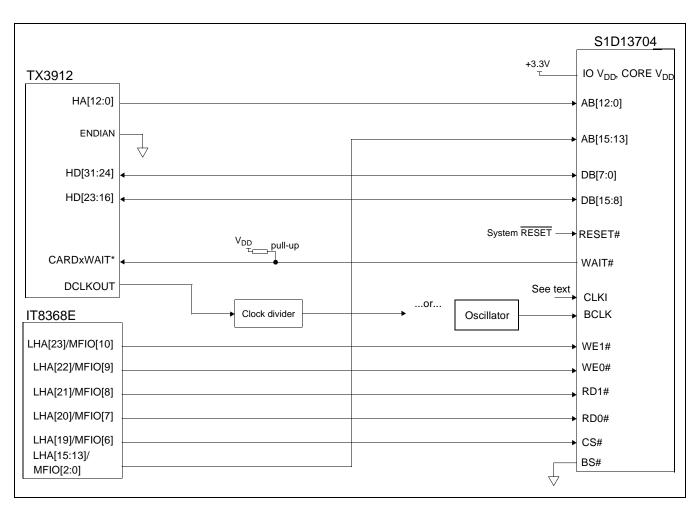

Interfacing to the Toshiba MIPS TX3912 Processor

Power Consumption

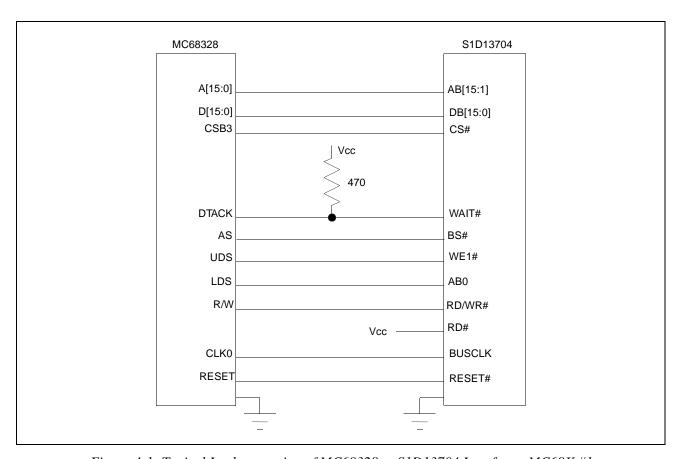

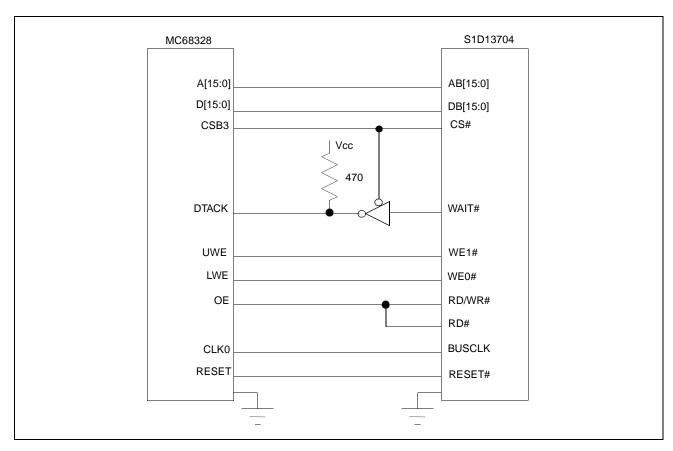

Interfacing to the Motorola MC68328 Microprocessor

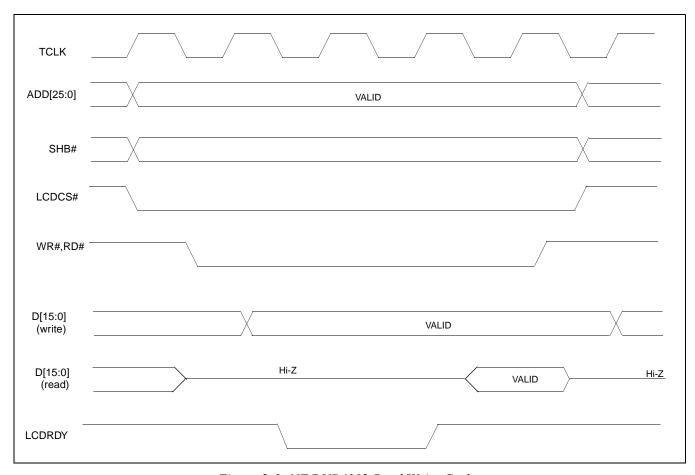

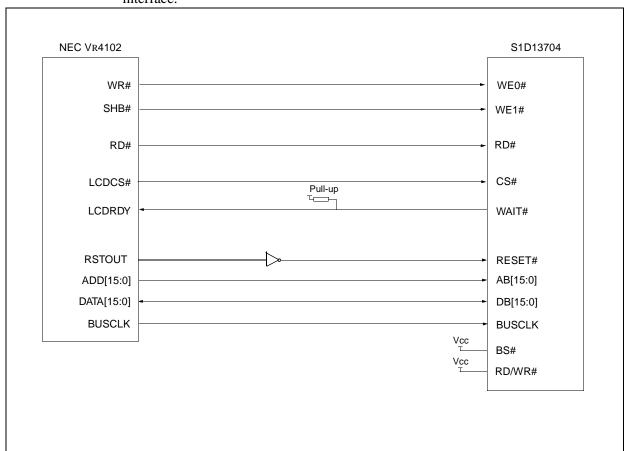

Interfacing to the NEC VR4102 Microprocessor

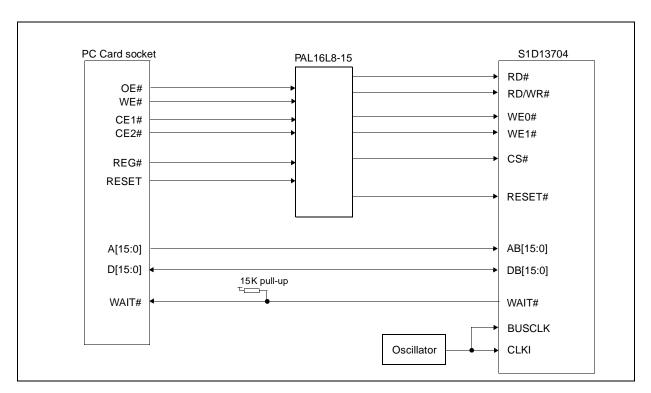

Interfacing the S1D13704 to the PC Card Bus

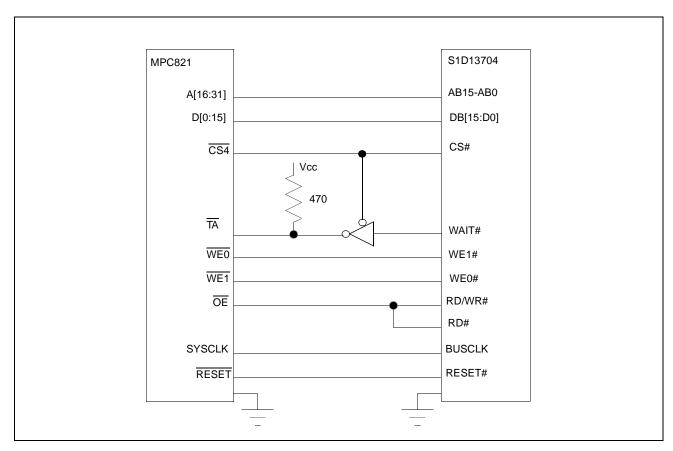

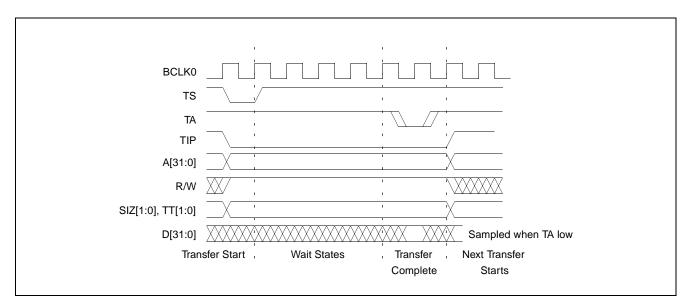

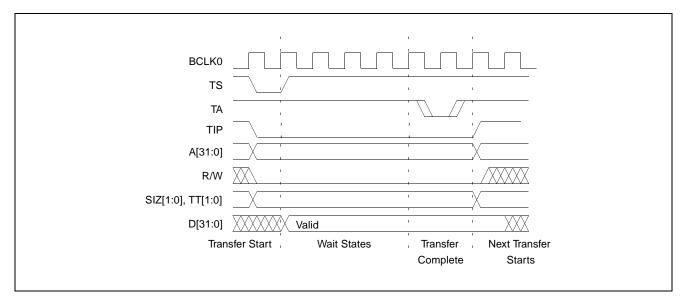

Interfacing to the Motorola MPC821 Microprocessor

Interfacing to the Motorola MCF5307 Microprocessor

Interfacing to the Philips MIPS PR31500/PR31700 Processor

S5U13704/5-TMPR3912/22U CPU Module

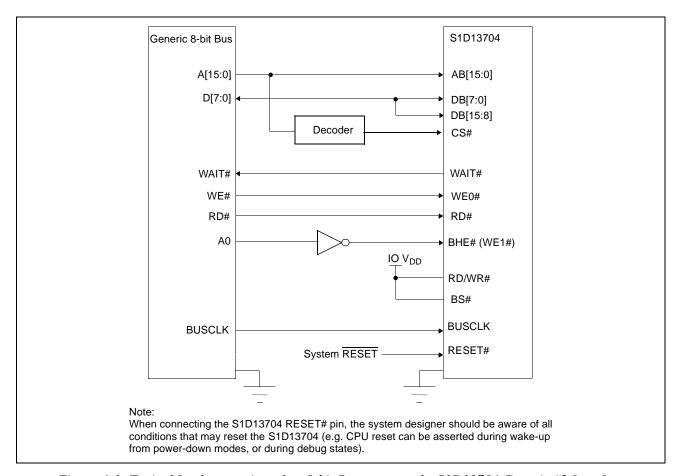

Interfacing to an 8-Bit Processor

THIS PAGE LEFT BLANK

# GRAPHICS S1D13704

February 2001

### S1D13704 EMBEDDED MEMORY COLOR LCD CONTROLLER

### **■** DESCRIPTION

The S1D13704 is a color/monochrome LCD graphics controller with an embedded 40K Byte SRAM display buffer. The high integration of the S1D13704 provides a low cost, low power, single chip solution to meet the requirements of embedded markets such as Office Automation equipment, Mobile Communications devices, and Palmsize PCs where board size and battery life are major concerns.

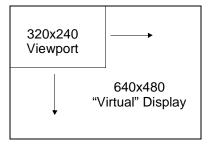

Products requiring a "Portrait" display can take advantage of the Hardware Portrait Mode feature of the S1D13704. Virtual and Split Screen are just some of the display modes supported. The above features, combined with the Operating System independence of the S1D13704, make it the ideal solution for a wide variety of applications.

#### **■** FEATURES

### **Memory Interface**

• Embedded 40K byte SRAM display buffer.

#### **CPU Interface**

Direct support of the following interfaces:

Hitachi SH-3.

Hitachi SH-4.

Motorola M68K.

MPU bus interface with programmable READY.

- · Direct memory mapping of internal registers.

- CPU write buffer.

#### **Display Support**

- 4/8-bit monochrome LCD interface.

- 4/8-bit color LCD interface.

- Single-panel, single-drive passive displays.

- Dual-panel, dual-drive passive displays.

- Active Matrix TFT / TFD interface.

- Register level suport for EL panels.

- Example resolutions:

640x480 at a color depth of 1 bpp 640x240 at a color depth of 2 bpp 320x240 at a color depth of 4 bpp 240x160 at a color depth of 8 bpp

#### **Power Down Modes**

- Hardware and software Suspend modes.

- LCD power-down sequencing.

### **Display Modes**

- Hardware Portrait Mode: direct hardware rotation of display image for portrait mode display.

- 1/2/4 bit-per-pixel (bpp), 2/4/16-level grayscale display.

- 1/2/4/8 bit-per-pixel, 2/4/16/256-level color display.

- Up to 16 shades of gray by FRM on monochrome passive LCD panels.

- 256 simultaneous of 4096 colors on color passive and active matrix LCD panels.

- Split screen display for all panel modes allows two different images to be simultaneously displayed.

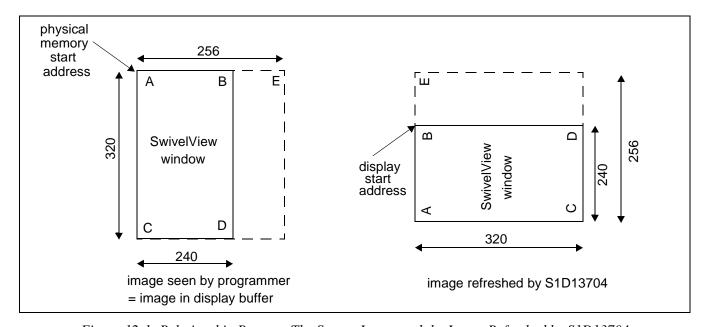

- Virtual display support (displays images larger than the panel size through the use of panning).

#### **Clock Source**

- Single clock input for both pixel and memory clocks.

- The S1D13704 clock source can be internally divided down for a higher frequency clock input.

- Dynamic switching of memory clocks in portrait mode.

### **General Purpose IO Pins**

• Five General Purpose Input / Output pins available.

### **Operating Voltage**

• 2.7 volts to 5.5 volts.

#### **Package**

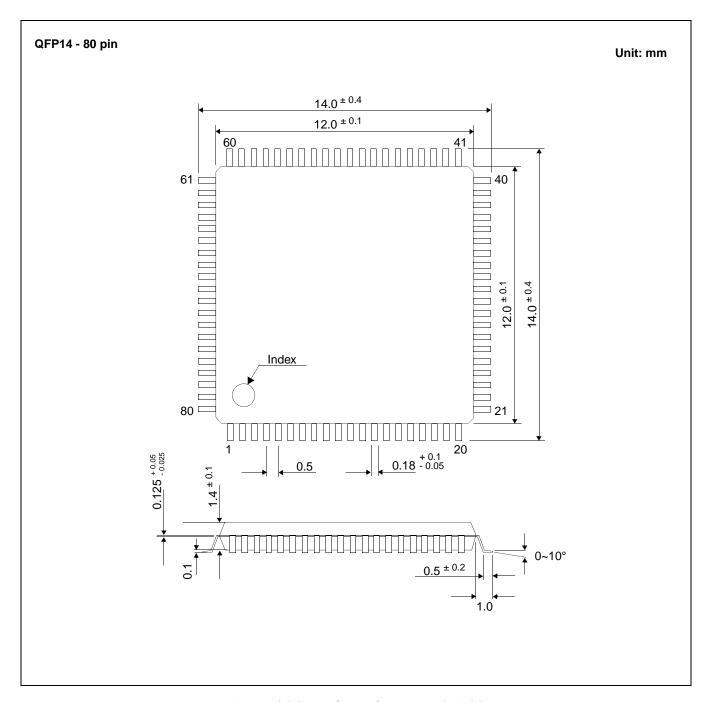

• 80-pin QFP14 surface mount package.

X26A-C-001-07

## **EPSON**°

### S1D13704

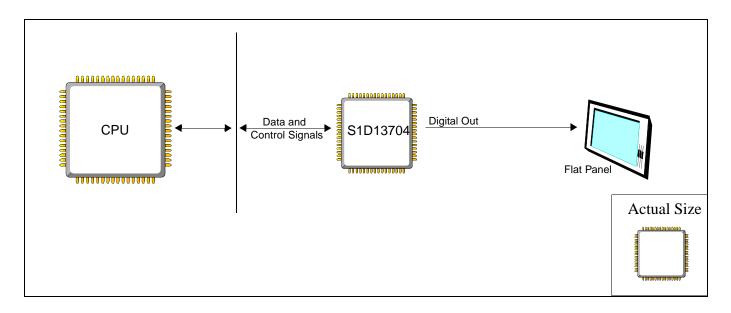

### ■ SYSTEM BLOCK DIAGRAM

# CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS:

- S1D13704 Technical Manual

- S5U13704 Evaluation Boards

- Windows<sup>®</sup> CE Display Driver

- CPU Independent Software Utilities

#### Japan

Seiko Epson Corporation Electronic Devices Marketing Division 421-8, Hino, Hino-shi Tokyo 191-8501, Japan Tel: 042-587-5812 Fax: 042-587-5564 http://www.epson.co.jp

#### **Hong Kong**

Epson Hong Kong Ltd. 20/F., Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: 2585-4600 Fax: 2827-4346

#### **North America**

Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com

### Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110

# FOR SYSTEM INTEGRATION SERVICES FOR WINDOWS® CE CONTACT:

Epson Research & Development, Inc. Suite #320 - 11120 Horseshoe Way Richmond, B.C., Canada V7A 5H7

Tel: (604) 275-5151 Fax: (604) 275-2167 Email: wince@erd.epson.com

http://www.erd.epson.com

#### Taiwan, R.O.C.

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan, R.O.C.

Tel: 02-2717-7360 Fax: 02-2712-9164

### Singapore

Fax: 334-2716

Epson Singapore Pte., Ltd. No. 1 Temasek Avenue #36-00 Millenia Tower Singapore, 039192 Tel: 337-7911

Copyright @1998, 2001 Epson Research and Development, Inc. All rights reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft, Windows, and the Windows CE Logo are registered trademarks of Microsoft Corporation.

2 X26A-C-001-07

### S1D13704 Embedded Memory LCD Controller

# **Hardware Functional Specification**

Document Number: X26A-A-001-04

Copyright © 1998, 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

THIS PAGE LEFT BLANK

# **Table of Contents**

| 1 | Introduc   | tion                                         |

|---|------------|----------------------------------------------|

|   | 1.1 Sco    | pe                                           |

|   | 1.2 Ove    | erview Description                           |

| 2 | Features   |                                              |

|   | 2.1 Inte   | grated Frame Buffer                          |

|   | 2.2 CPI    | J Interface                                  |

|   | 2.3 Dis    | play Support                                 |

|   | 2.4 Dis    | play Modes                                   |

|   | 2.5 Clo    | ck Source                                    |

|   | 2.6 Mis    | cellaneous                                   |

|   | 2.7 Pac    | kage                                         |

| 3 | Typical \$ | System Implementation Diagrams               |

| 4 |            | nal Block Diagram ........................15 |

|   |            | ctional Block Descriptions                   |

|   | 4.1.1      | Host Interface                               |

|   | 4.1.2      | Memory Controller                            |

|   | 4.1.3      | Sequence Controller                          |

|   | 4.1.4      | Look-Up Table                                |

|   | 4.1.5      | LCD Interface                                |

|   | 4.1.6      | Power Save                                   |

| 5 | Pins       |                                              |

|   | 5.1 Pine   | out Diagram                                  |

|   | 5.2 Pin    | Description                                  |

|   | 5.2.1      | Host Interface                               |

|   | 5.2.2      | LCD Interface                                |

|   | 5.2.3      | Clock Input                                  |

|   | 5.2.4      | Miscellaneous                                |

|   | 5.2.5      | Power Supply                                 |

|   | 5.3 Sun    | nmary of Configuration Options               |

|   | 5.4 Hos    | t Bus Interface Pin Mapping                  |

|   | 5.5 LC     | D Interface Pin Mapping                      |

| 6 | D.C. Cha   | racteristics                                 |

| 7 | A.C. Cha   | ıracteristics                                |

|   | 7.1 Bus    | Interface Timing                             |

|   | 7.1.1      | SH-4 Interface Timing                        |

|   | 7.1.2      | SH-3 Interface Timing                        |

|   | 7.1.3      | Motorola M68K #1 Interface Timing            |

|    | 7.1.4      | Motorola M68K #2 Interface Timing                      |

|----|------------|--------------------------------------------------------|

|    | 7.1.5      | Generic #1 Interface Timing                            |

|    | 7.1.6      | Generic #2 Interface Timing                            |

|    | 7.2 Clock  | k Input Requirements                                   |

|    | 7.3 Displ  | lay Interface                                          |

|    | 7.3.1      | Power On/Reset Timing                                  |

|    | 7.3.2      | Power Down/Up Timing                                   |

|    | 7.3.3      | Single Monochrome 4-Bit Panel Timing                   |

|    | 7.3.4      | Single Monochrome 8-Bit Panel Timing                   |

|    | 7.3.5      | Single Color 4-Bit Panel Timing                        |

|    | 7.3.6      | Single Color 8-Bit Panel Timing (Format 1)             |

|    | 7.3.7      | Single Color 8-Bit Panel Timing (Format 2)             |

|    | 7.3.8      | Dual Monochrome 8-Bit Panel Timing                     |

|    | 7.3.9      | Dual Color 8-Bit Panel Timing                          |

|    | 7.3.10     | 9/12-Bit TFT/D-TFD Panel Timing                        |

| 8  | Registers  | 5                                                      |

|    | 8.1 Regis  | ster Mapping                                           |

|    | 8.2 Regis  | ster Descriptions                                      |

| 9  | Frame Ra   | te Calculation                                         |

| 10 | Display D  | ata Formats                                            |

| 11 | Look-Up    | Table Architecture ..........................72        |

|    | 11.1 Gray  | Shade Display Modes                                    |

|    |            | r Display Modes                                        |

| 12 | SwivelVie  | •w™                                                    |

|    | 12.1 Defa  | ult SwivelView Mode                                    |

|    | 12.1.1     | How to Set Up Default SwivelView Mode                  |

|    | 12.2 Alter | nate SwivelView Mode                                   |

|    | 12.2.1     | How to Set Up Alternate SwivelView Mode                |

|    | 12.3 Com   | parison Between Default and Alternate SwivelView Modes |

|    | 12.4 Swiv  | elView Mode Limitations                                |

| 13 | Power Sa   | ve Modes                                               |

|    | 13.1 Softv | vare Power Save Mode                                   |

|    | 13.2 Hard  | ware Power Save Mode                                   |

|    | 13.3 Powe  | er Save Mode Function Summary                          |

|    |            | l Power Up/Down Sequence                               |

|    | 13.5 Turn  | ing Off BCLK Between Accesses                          |

|    | 13.6 Clock | k Requirements                                         |

| 14 | Mechanic   | al Data                                                |

# **List of Tables**

| Table 5-1:  | Summary of Power On/Reset Options                |

|-------------|--------------------------------------------------|

| Table 5-2:  | Host Bus Interface Pin Mapping                   |

| Table 5-3:  | LCD Interface Pin Mapping                        |

| Table 6-1:  | Absolute Maximum Ratings                         |

| Table 6-2:  | Recommended Operating Conditions                 |

|             | Input Specifications                             |

| Table 6-4:  | Output Specifications                            |

| Table 7-1:  | SH-4 Timing                                      |

| Table 7-2:  | SH-3 Bus Timing                                  |

| Table 7-3:  | M68K #1 Bus Timing (MC68000)                     |

| Table 7-4:  | M68K #2 Timing (MC68030)                         |

| Table 7-5:  | Generic #1 Timing                                |

| Table 7-6:  | Generic #2 Timing                                |

| Table 7-7:  | Clock Input Requirements                         |

| Table 7-8:  | Power Down/Up Timing                             |

| Table 8-1:  | Panel Data Format                                |

| Table 8-2:  | Gray Shade/Color Mode Selection                  |

| Table 8-3:  | High Performance Selection                       |

| Table 8-4:  | Inverse Video Mode Select Options                |

| Table 8-5:  | Hardware Power Save/GPIO0 Operation              |

| Table 8-6:  | Software Power Save Mode Selection               |

| Table 8-7:  | Look-Up Table Access                             |

| Table 8-8:  | Selection of SwivelView Mode                     |

| Table 8-9:  | Selection of PCLK and MCLK in SwivelView Mode    |

| Table 11-1: | Look-Up Table Configurations                     |

| Table 12-1: | Default and Alternate SwivelView Mode Comparison |

| Table 13-1: | Power Save Mode Selection                        |

| Table 13-2: | Software Power Save Mode Summary                 |

| Table 13-3: | Hardware Power Save Mode Summary                 |

| Table 13-4: | Power Save Mode Function Summary                 |

| Table 13-5: | S1D13704 Internal Clock Requirements             |

THIS PAGE LEFT BLANK

# **List of Figures**

| Figure 3-1:  | Typical System Diagram (SH-4 Bus)                      |

|--------------|--------------------------------------------------------|

| Figure 3-2:  | Typical System Diagram (SH-3 Bus)                      |

| Figure 3-3:  | Typical System Diagram (M68K #1 Bus)                   |

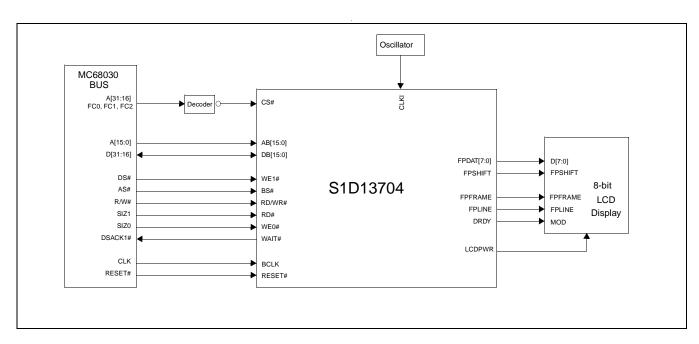

| Figure 3-4:  | Typical System Diagram (M68K #2 Bus)                   |

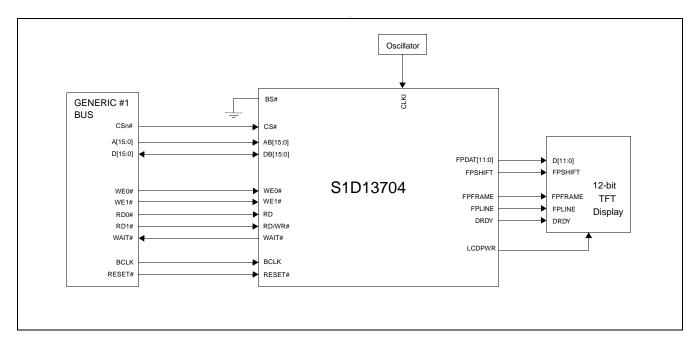

| Figure 3-5:  | Typical System Diagram (Generic #1 Bus)                |

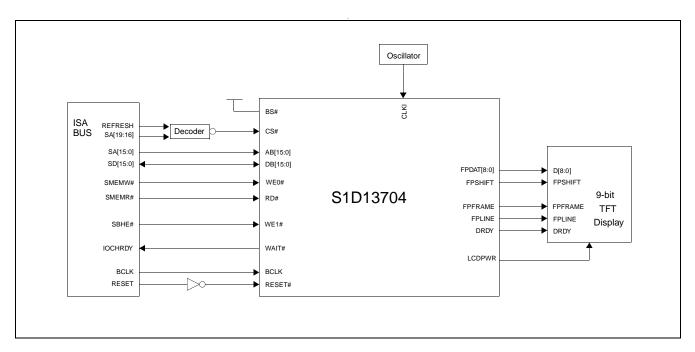

| Figure 3-6:  | Typical System Diagram (Generic #2 Bus - e.g. ISA Bus) |

| Figure 4-1:  | System Block Diagram Showing Data Paths                |

| Figure 5-1:  | Pinout Diagram                                         |

| Figure 7-1:  | SH-4 Timing                                            |

| Figure 7-2:  | SH-3 Bus Timing                                        |

| Figure 7-3:  | M68K #1 Bus Timing (MC68000)                           |

| Figure 7-4:  | M68K #2 Timing (MC68030)                               |

| Figure 7-5:  | Generic #1 Timing                                      |

| Figure 7-6:  | Generic #2 Timing                                      |

| Figure 7-7:  | Clock Input Requirements                               |

| Figure 7-8:  | LCD Panel Power On/Reset Timing                        |

| Figure 7-9:  | Power Down/Up Timing                                   |

| Figure 7-10: | Single Monochrome 4-Bit Panel Timing                   |

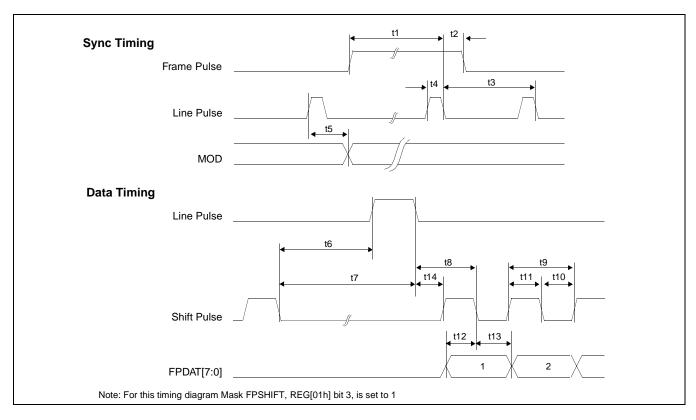

| Figure 7-11: | Single Monochrome 4-Bit Panel A.C. Timing              |

| Figure 7-12: | Single Monochrome 8-Bit Panel Timing                   |

| Figure 7-13: | Single Monochrome 8-Bit Panel A.C. Timing              |

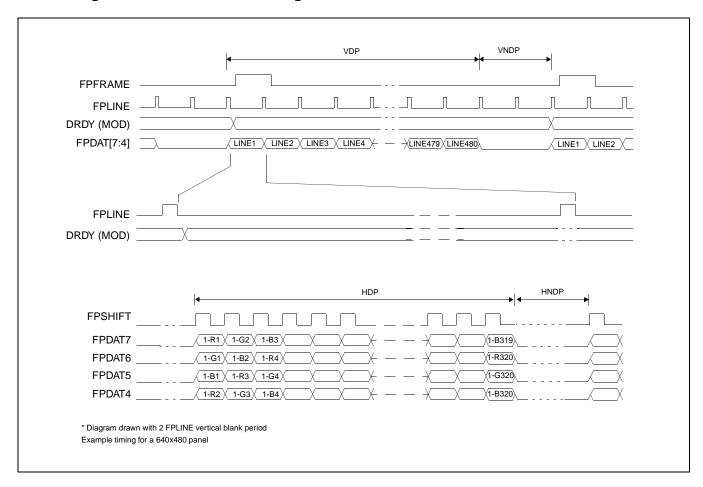

| Figure 7-14: | Single Color 4-Bit Panel Timing                        |

| Figure 7-15: | Single Color 4-Bit Panel A.C. Timing                   |

| Figure 7-16: | Single Color 8-Bit Panel Timing (Format 1)             |

| Figure 7-17: | Single Color 8-Bit Panel A.C. Timing (Format 1)        |

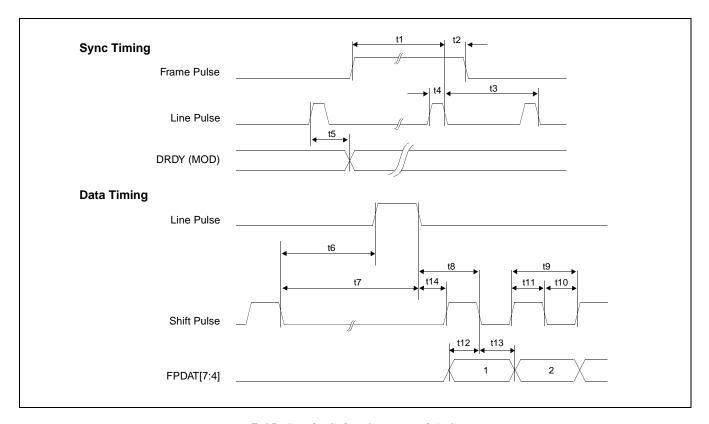

| Figure 7-18: | Single Color 8-Bit Panel Timing (Format 2)             |

| Figure 7-19: | Single Color 8-Bit Panel A.C. Timing (Format 2)        |

| Figure 7-20: | Dual Monochrome 8-Bit Panel Timing                     |

| Figure 7-21: | Dual Monochrome 8-Bit Panel A.C. Timing                |

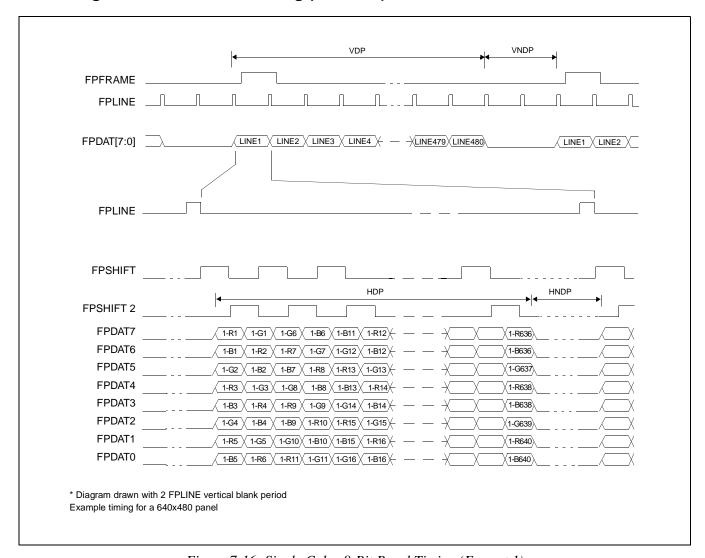

| Figure 7-22: | Dual Color 8-Bit Panel Timing                          |

| Figure 7-23: | Dual Color 8-Bit Panel A.C. Timing                     |

| Figure 7-24: | 12-Bit TFT/D-TFD Panel Timing                          |

| Figure 7-25: | TFT/D-TFD A.C. Timing                                  |

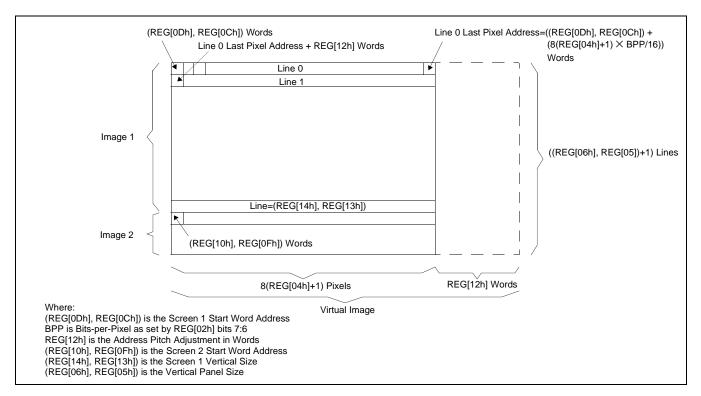

| Figure 8-1:  | Screen-Register Relationship, Split Screen             |

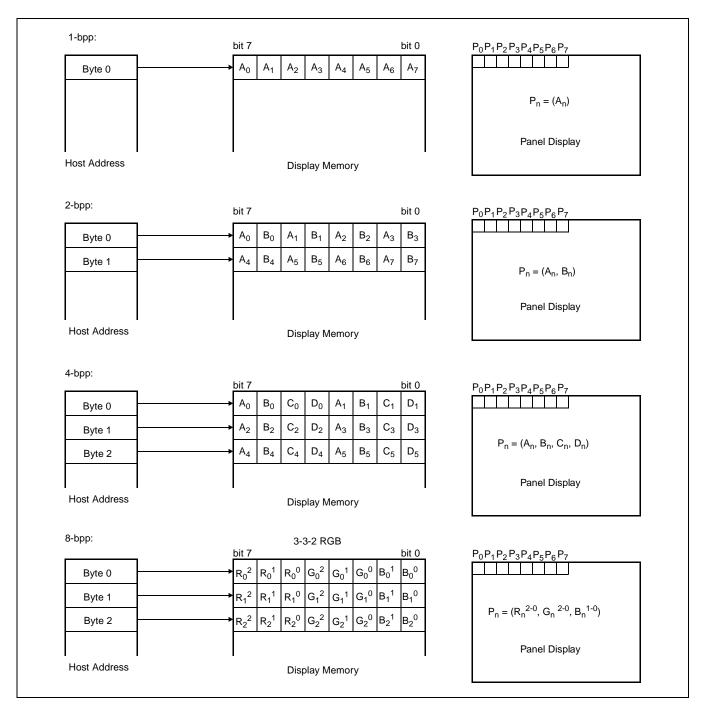

| Figure 10-1: | 1/2/4/8 Bit-Per-Pixel Display Data Memory Organization |

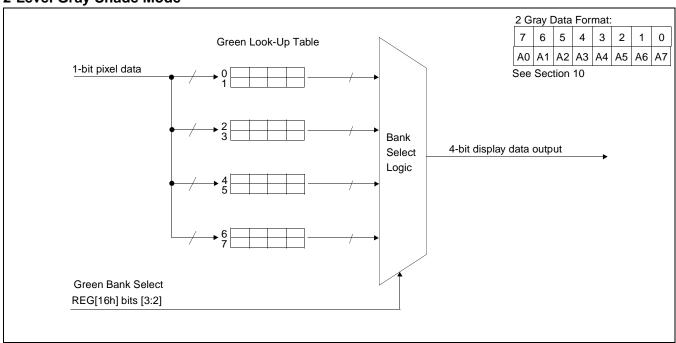

| Figure 11-1: | 2-Level Gray-Shade Mode Look-Up Table Architecture     |

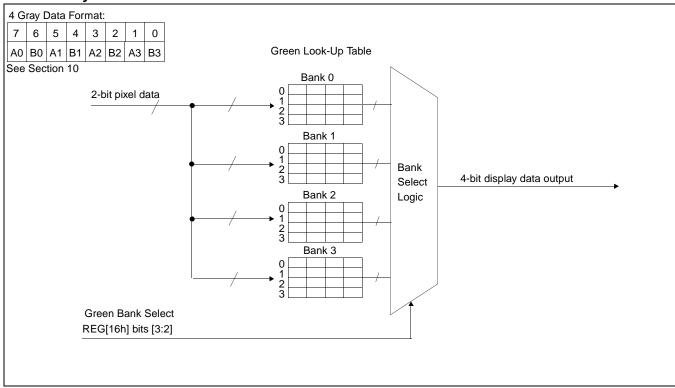

| Figure 11-2: | 4-Level Gray-Shade Mode Look-Up Table Architecture     |

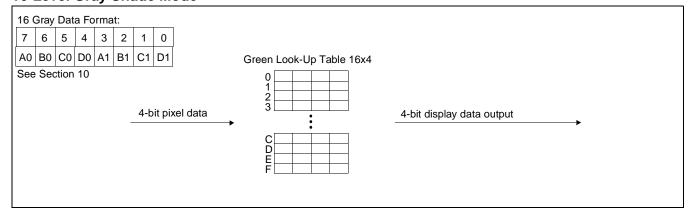

| Figure 11-3: 16-Level Gray-Shade Mode Look-Up Table Architecture                         |

|------------------------------------------------------------------------------------------|

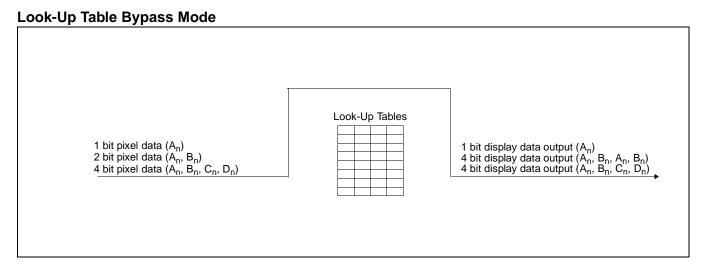

| Figure 11-4: Look-Up Table Bypass Mode Architecture                                      |

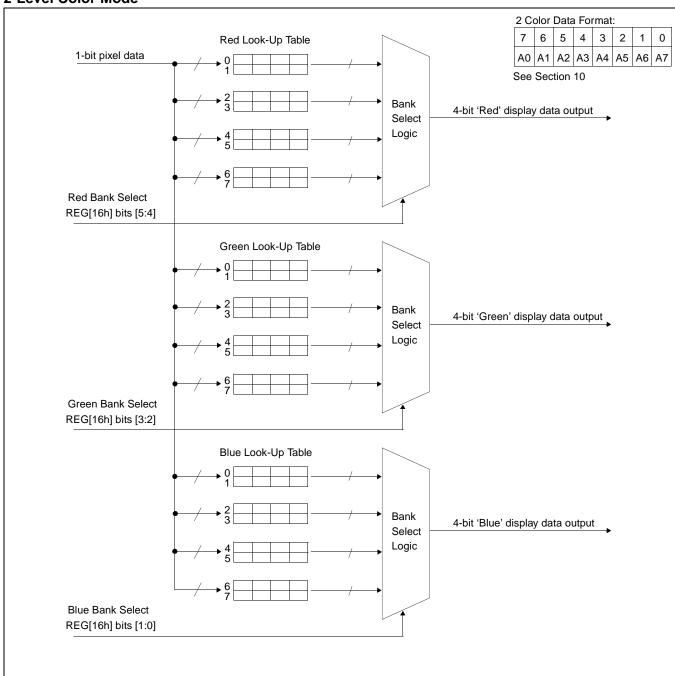

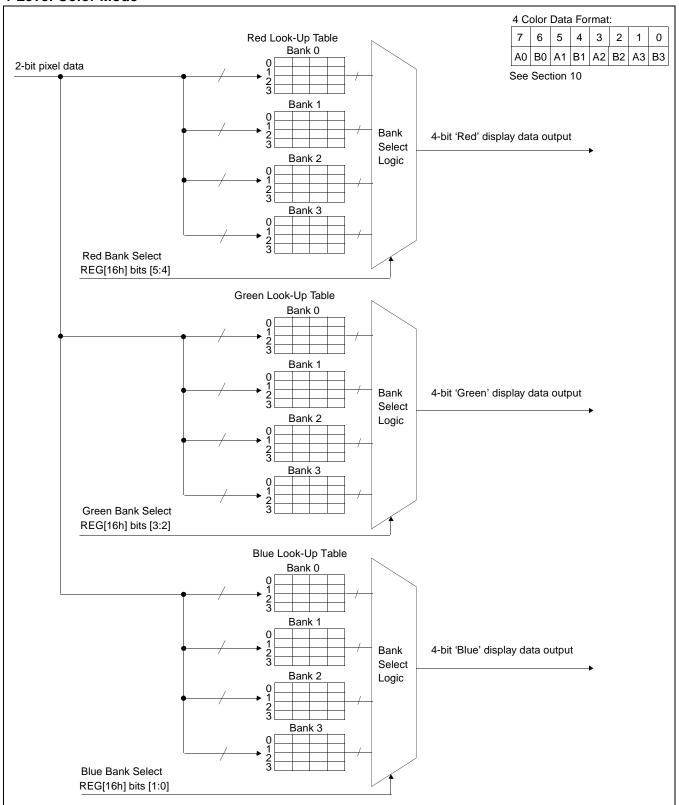

| Figure 11-5: 2-Level Color Look-Up Table Architecture                                    |

| Figure 11-6: 4-Level Color Mode Look-Up Table Architecture                               |

| Figure 11-7: 16-Level Color Mode Look-Up Table Architecture                              |

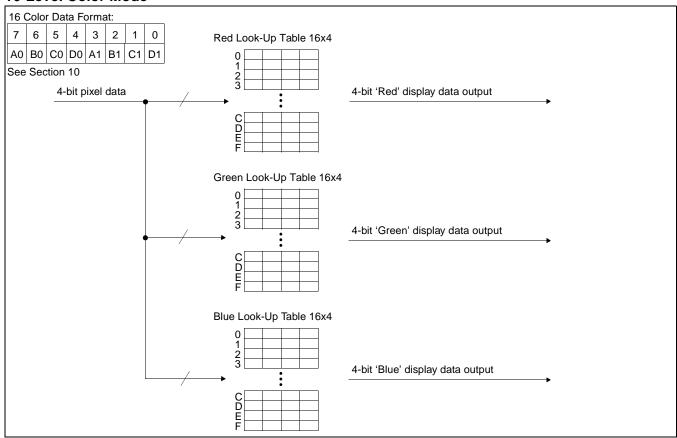

| Figure 11-8: 256-Level Color Mode Look-Up Table Architecture                             |

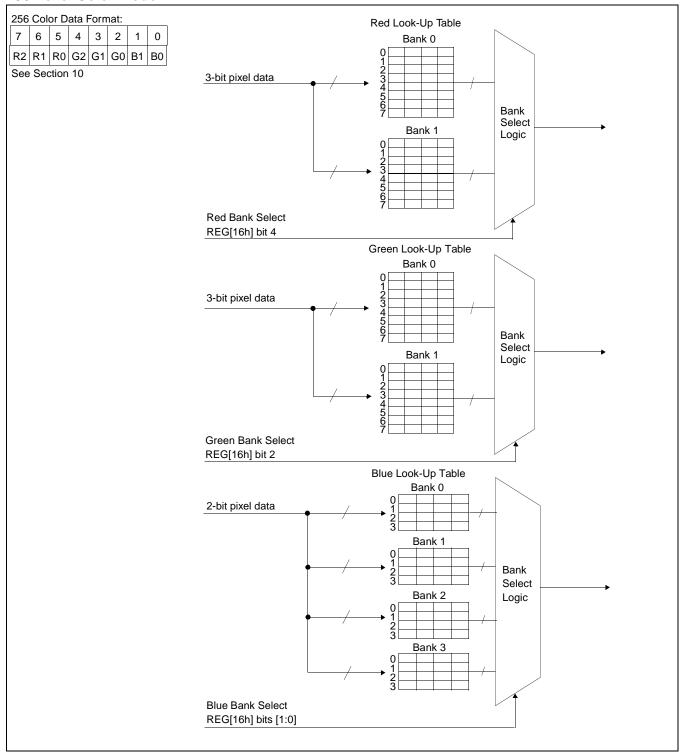

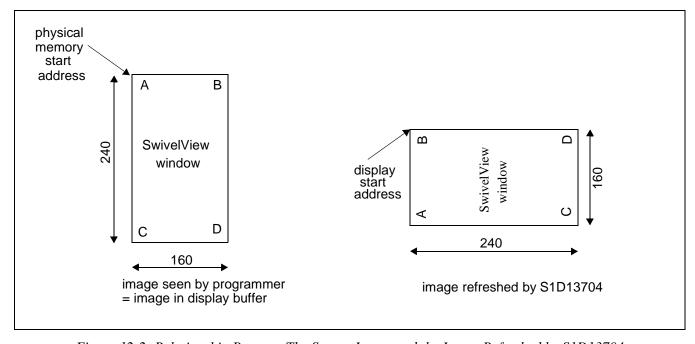

| Figure 12-1: Relationship Between The Screen Image and the Image Refreshed by S1D13704   |

| Figure 12-2: Relationship Between The Screen Image and the Image Refreshed by S1D1370481 |

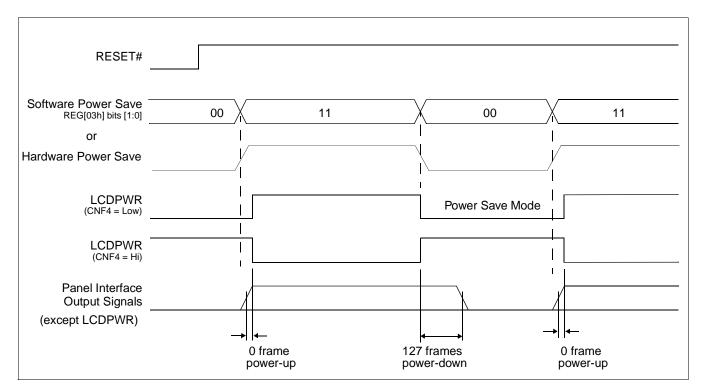

| Figure 13-1: Panel On/Off Sequence                                                       |

| Figure 14-1: Mechanical Drawing QFP14                                                    |

### 1 Introduction

### 1.1 Scope

This is the Functional Specification for the S1D13704 Embedded Memory LCD Controller Chip. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

Please check the Epson Electronics America website at http://www.eea.epson.com for the latest revision of this document before beginning any development.

We appreciate your comments on our documentation. Please contact us via email at techpubs@erd.epson.com.

### 1.2 Overview Description

The S1D13704 is a color / monochrome LCD graphics controller with an embedded 40K Byte SRAM display buffer. The high integration of the S1D13704 provides a low cost, low power, single chip solution to meet the requirements of embedded markets such as Office Automation equipment, Mobile Communications devices, and Hand-Held PCs where board size and battery life are major concerns.

Products requiring a "Portrait" display can take advantage of the Swivelview<sup>TM</sup> (90° Hardware Rotate) feature of the S1D13704. Virtual and Split Screen are just some of the display modes supported. The above features, combined with the Operating System independence of the S1D13704, make it the ideal solution for a wide variety of applications.

### 2 Features

### 2.1 Integrated Frame Buffer

• Embedded 40K byte SRAM display buffer.

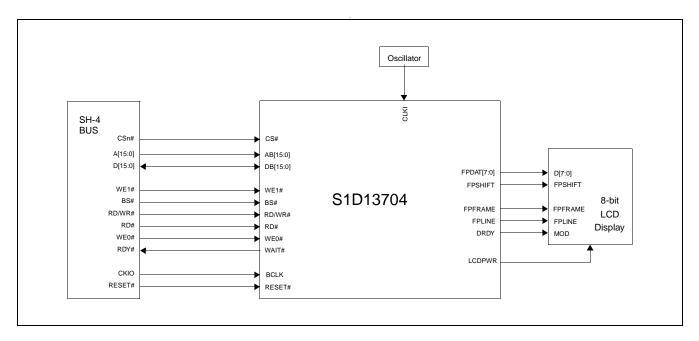

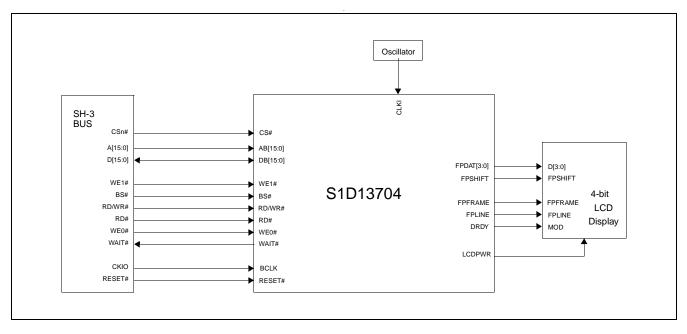

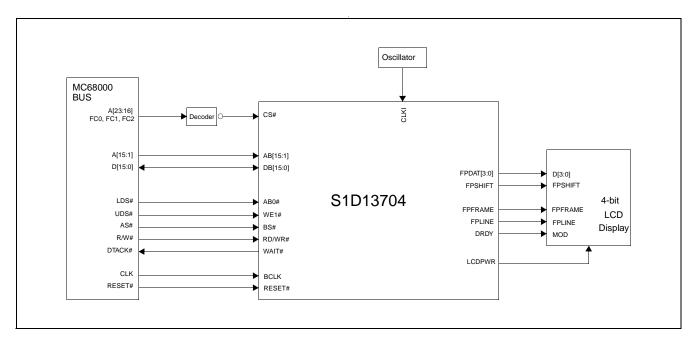

### 2.2 CPU Interface

• Direct support of the following interfaces:

Hitachi SH-3.

Hitachi SH-4.

Motorola M68K.

MPU bus interface using WAIT# signal.

- Direct memory mapping of internal registers.

- Single level CPU write buffer.

- Registers are mapped into upper 32 bytes of 64K byte address space.

- The complete 40K byte frame buffer is directly and contiguously available through the 16-bit address bus.

### 2.3 Display Support

- 4/8-bit monochrome LCD interface.

- 4/8-bit color LCD interface.

- Single-panel, single-drive passive displays.

- Dual-panel, dual-drive passive displays.

- Active Matrix TFT / D-TFD interface

- Register level support for EL panels.

- Example resolutions:

640x480 at a color depth of 1 bpp 640x240 at a color depth of 2 bpp 320x240 at a color depth of 4 bpp 240x160 at a color depth of 8 bpp

### 2.4 Display Modes

- SwivelView<sup>TM</sup>: direct 90° hardware rotation of display image for portrait mode display.

- 1/2/4 bit-per-pixel (bpp), 2/4/16-level grayshade display.

- 1/2/4/8 bit-per-pixel, 2/4/16/256-level color display.

- Up to 16 shades of gray by FRM on monochrome passive LCD panels; a 16x4 Look-Up-Table is used to map 1/2/4-bpp modes into these shades.

- 256 simultaneous of 4096 colors on color passive and active matrix LCD panels; three 16x4 Look-Up Tables are used to map 1/2/4/8-bpp modes into these colors.

- Split screen display for all landscape panel modes allows two different images to be simultaneously displayed.

- Virtual display support (displays images larger than the panel size through the use of panning).

### 2.5 Clock Source

- Maximum operating clock (CLK) frequency of 25MHz.

- Operating clock (CLK) is derived from CLKI input.

• Pixel Clock (PCLK) and Memory Clock (MCLK) are derived from CLK.

### 2.6 Miscellaneous

- Hardware/Software Video Invert.

- Software Power Save mode.

- Hardware Power Save mode.

- LCD power-down sequencing.

- 5 General Purpose Input/Output pins are available.

- GPIO0 is available if Hardware Power Save is not required.

- GPIO[4:1] are available if upper LCD data pins (FPDAT[11:8]) are not required for TFT/D-TFD support or Hardware Video Invert.

- IO Operates from 3.0 volts to 5.5 volts

- Core operates from 3.0 volts to 3.6 volts.

### 2.7 Package

• 80 pin QFP14 package.

# 3 Typical System Implementation Diagrams

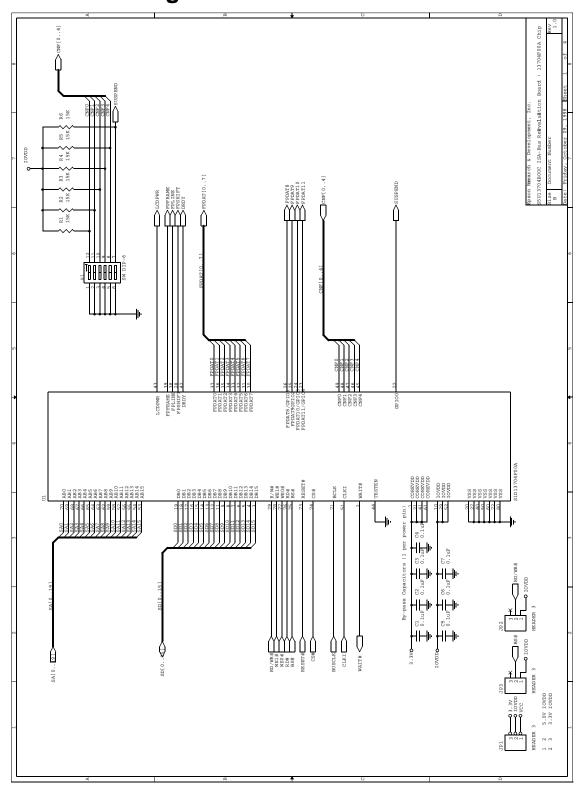

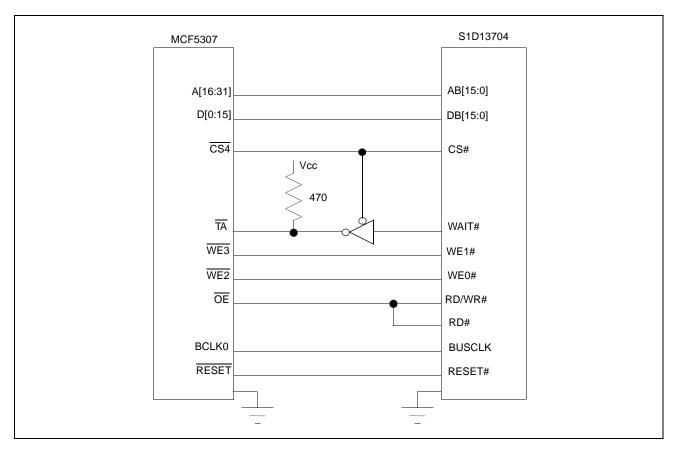

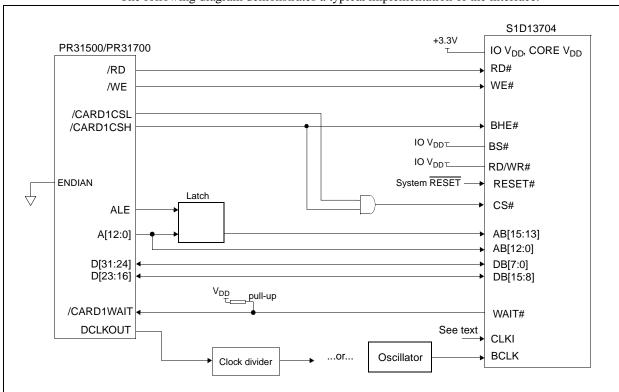

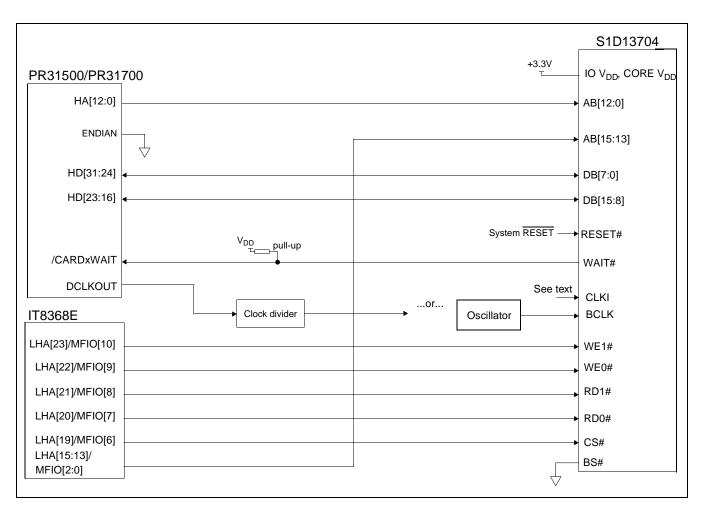

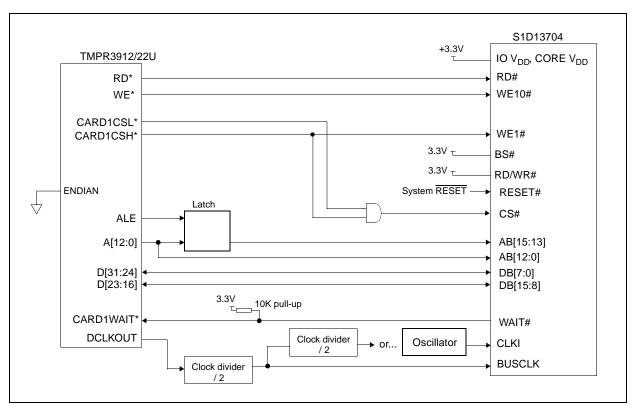

Figure 3-1: Typical System Diagram (SH-4 Bus)

Figure 3-2: Typical System Diagram (SH-3 Bus)

Figure 3-3: Typical System Diagram (M68K #1 Bus)

Figure 3-4: Typical System Diagram (M68K #2 Bus)

Figure 3-5: Typical System Diagram (Generic #1 Bus)

Figure 3-6: Typical System Diagram (Generic #2 Bus - e.g. ISA Bus)

# 4 Functional Block Diagram

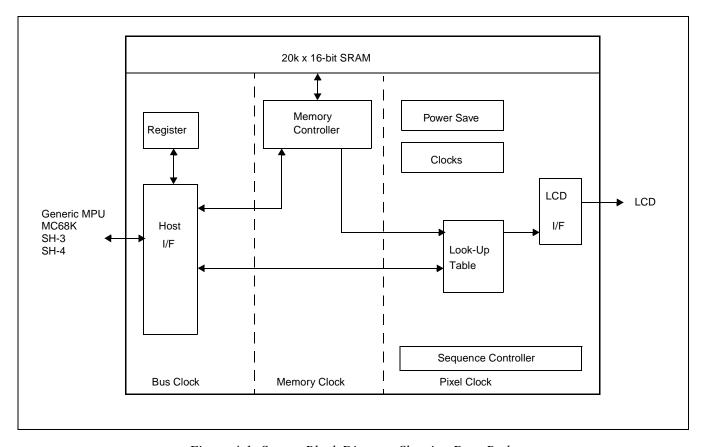

Figure 4-1: System Block Diagram Showing Data Paths

### 4.1 Functional Block Descriptions

### 4.1.1 Host Interface

The Host Interface provides the means for the CPU/MPU to communicate with the display memory and internal registers.

### 4.1.2 Memory Controller

The Memory Controller arbitrates between CPU accesses and display refresh accesses. It also generates the necessary signals to control the SRAM frame buffer.

### 4.1.3 Sequence Controller

The Sequence Controller controls data flow from the Memory Controller through the Look-Up Table and to the LCD Interface. It also generates memory addresses for display refresh accesses.

### 4.1.4 Look-Up Table

The Look-Up Table contains three 16x4 Look-Up Tables or palettes, one for each primary color. In monochrome mode only one of these Look-Up Tables is used.

### 4.1.5 LCD Interface

The LCD Interface performs frame rate modulation for passive LCD panels. It also generates the correct data format and timing control signals for various LCD and TFT/D-TFD panels.

### 4.1.6 Power Save

Power Save contains the power save mode circuitry.

### 5 Pins

### 5.1 Pinout Diagram

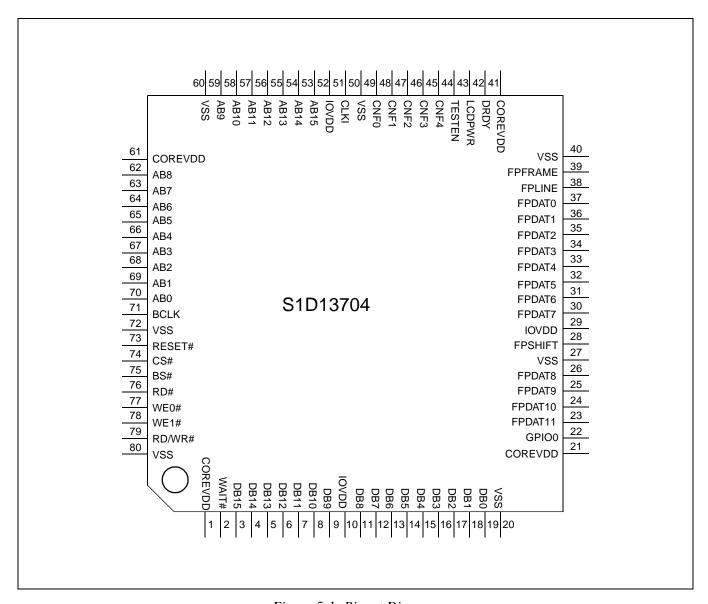

Figure 5-1: Pinout Diagram

### Note

Package type: 80 pin surface mount QFP14

### 5.2 Pin Description

### Key:

I = Input

O = Output

I/O = Bi-Directional (Input/Output)

P = Power pin

C = CMOS level input

CD = CMOS level input with pull down resistor (typical values of  $100K\Omega/180K\Omega$  at 5V/3.3V respectively)

CS = CMOS level Schmitt input

COx = CMOS output driver, x denotes driver type (1=3/-1.5mA, 2=6/-3mA, 3=12/-6mA)

TSx = Tri-state CMOS output driver, x denotes driver type (1=3/-1.5mA, 2=6/-3mA, 3=12/-6mA)

TSxD = Tri-state CMOS output driver with pull down resistor (typical values of  $100K\Omega/180K\Omega$  at 5V/3.3V

respectively), x denotes driver type (1=3/-1.5mA, 2=6/-3mA, 3=12/-6mA)

CNx = CMOS low-noise output driver, x denotes driver type (1=3/-1.5mA, 2=6/-3mA, 3=12/-6mA)

### 5.2.1 Host Interface

| Pin Names | Туре | Pin#                                                                | Cell  | RESET#<br>State   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|------|---------------------------------------------------------------------|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AB0       | I    | 70                                                                  | CS    | Input             | <ul> <li>This pin has multiple functions.</li> <li>For SH-3/SH-4 mode, this pin inputs system address bit 0 (A0).</li> <li>For MC68K #1, this pin inputs the lower data strobe (LDS#).</li> <li>For MC68K #2, this pin inputs system address bit 0 (A0).</li> <li>For Generic #1, this pin inputs system address bit 0 (A0).</li> <li>For Generic #2, this pin inputs system address bit 0 (A0).</li> </ul>                                                                                                                |

| AB[15:1]  | I    | 53, 54, 55,<br>56, 57, 58,<br>59, 62, 63,                           | С     | Input             | See "Host Bus Interface Pin Mapping" for summary.  These pins input the system address bits 15 through 1 (A[15:1]).                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |      | 64, 65, 66,<br>67, 68, 69                                           |       |                   | (/ · ( · ( · ( · ( · ( · ( · ( · ( · ( ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DB[15:0]  | I/O  | 3, 4, 5, 6, 7,<br>8, 9, 11, 12,<br>13, 14, 15,<br>16, 17, 18,<br>19 | C/TS2 | High<br>Impedance | <ul> <li>These pins have multiple functions.</li> <li>For SH-3/SH-4 mode, these pins are connected to [D15:0].</li> <li>For MC68K #1, these pins are connected to D[15:0].</li> <li>For MC68K #2, these pins are connected to D[31:16] for a 32-bit device (e.g. MC68030) or D[15:0] for a 16-bit device (e.g. MC68340).</li> <li>For Generic #1, these pins are connected to D[15:0].</li> <li>For Generic #2, these pins are connected to D[15:0].</li> <li>See "Host Bus Interface Pin Mapping" for summary.</li> </ul> |

| Pin Names | Туре | Pin # | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|------|-------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE0#      | ı    | 77    | CS   | Input           | <ul> <li>This pin has multiple functions.</li> <li>For SH-3/SH-4 mode, this pin inputs the write enable signal for the lower data byte (WE0#).</li> <li>For MC68K #1, this pin must be tied to IO V<sub>DD</sub></li> <li>For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).</li> <li>For Generic #1, this pin inputs the write enable signal for the lower data byte (WE0#).</li> <li>For Generic #2, this pin inputs the write enable signal (WE#)</li> <li>See "Host Bus Interface Pin Mapping" for summary.</li> </ul>                        |

| WE1#      | I    | 78    | CS   | Input           | <ul> <li>This pin has multiple functions.</li> <li>For SH-3/SH-4 mode, this pin inputs the write enable signal for the upper data byte (WE1#).</li> <li>For MC68K #1, this pin inputs the upper data strobe (UDS#).</li> <li>For MC68K #2, this pin inputs the data strobe (DS#).</li> <li>For Generic #1, this pin inputs the write enable signal for the upper data byte (WE1#).</li> <li>For Generic #2, this pin inputs the byte enable signal for the high data byte (BHE#).</li> <li>See "Host Bus Interface Pin Mapping" for summary.</li> </ul> |

| CS#       | I    | 74    | С    | Input           | This pin inputs the chip select signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BCLK      | I    | 71    | С    | Input           | This pin inputs the system bus clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BS#       | I    | 75    | CS   | Input           | This pin has multiple functions.  • For SH-3/SH-4 mode, this pin inputs the bus start signal (BS#).  • For MC68K #1, this pin inputs the address strobe (AS#).  • For MC68K #2, this pin inputs the address strobe (AS#).  • For Generic #1, this pin must be tied to V <sub>SS</sub> .  • For Generic #2, this pin must be tied to IO V <sub>DD</sub> .  See "Host Bus Interface Pin Mapping" for summary.                                                                                                                                             |

| RD/WR#    | ı    | 79    | CS   | Input           | <ul> <li>This pin has multiple functions.</li> <li>For SH-3/SH-4 mode, this pin inputs the RD/WR# signal. The S1D13704 needs this signal for early decode of the bus cycle.</li> <li>For MC68K #1, this pin inputs the R/W# signal.</li> <li>For MC68K #2, this pin inputs the R/W# signal.</li> <li>For Generic #1, this pin inputs the read command for the upper data byte (RD1#).</li> <li>For Generic #2, this pin must be tied to IO V<sub>DD</sub>.</li> <li>See "Host Bus Interface Pin Mapping" for summary.</li> </ul>                        |

| Pin Names | Туре | Pin# | Cell | RESET#<br>State   | Description                                                                                                            |

|-----------|------|------|------|-------------------|------------------------------------------------------------------------------------------------------------------------|

|           |      |      |      |                   | This pin has multiple functions.                                                                                       |

|           |      |      |      |                   | For SH-3/SH-4 mode, this pin inputs the read signal (RD#).                                                             |

|           |      |      |      |                   | For MC68K #1, this pin must be tied to IO V <sub>DD</sub> .                                                            |

| RD#       | 1    | 76   | CS   | Input             | For MC68K #2, this pin inputs the bus size bit 1 (SIZ1).                                                               |

|           |      |      |      | ·                 | For Generic #1, this pin inputs the read command for the lower data byte (RD0#).                                       |

|           |      |      |      |                   | For Generic #2, this pin inputs the read command (RD#).                                                                |

|           |      |      |      |                   | See "Host Bus Interface Pin Mapping" for summary.                                                                      |

|           | 0    | ) 2  | TS2  | High<br>Impedance | This pin has multiple functions.                                                                                       |

|           |      |      |      |                   | For SH-3 mode, this pin outputs the wait request signal (WAIT#).                                                       |

|           |      |      |      |                   | For SH-4 mode, this pin outputs the device ready signal (RDY#).                                                        |

| WAIT#     |      |      |      |                   | <ul> <li>For MC68K #1, this pin outputs the data transfer<br/>acknowledge signal (DTACK#).</li> </ul>                  |

|           |      |      |      |                   | <ul> <li>For MC68K #2, this pin outputs the data transfer and<br/>size acknowledge bit 1 (DSACK1#).</li> </ul>         |

|           |      |      |      |                   | For Generic #1, this pin outputs the wait signal (WAIT#).                                                              |

|           |      |      |      |                   | For Generic #2, this pin outputs the wait signal (WAIT#).                                                              |

|           |      |      |      |                   | See "Host Bus Interface Pin Mapping" for summary.                                                                      |

| RESET#    | I    | 73   | cs   | 0                 | Active low input to set all internal registers to the default state and to force all signals to their inactive states. |

### 5.2.2 LCD Interface

| Pin Name    | Туре      | Pin #                                | Cell | RESET#<br>State | Description                                                                                                                                                                                                                                                                                                    |

|-------------|-----------|--------------------------------------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPDAT[7:0]  | 0         | 30, 31, 32,<br>33, 34, 35,<br>36, 37 | CN3  | 0               | Panel Data                                                                                                                                                                                                                                                                                                     |

| FPDAT[10:8] | O,<br>I/O | 24, 25, 26                           | CN3  | Input           | These pins have multiple functions.  • Panel Data bits [10:8] for TFT/D-TFD panels.  • General Purpose Input/Output pins GPIO[3:1].  These pins should be connected to IO V <sub>DD</sub> when unused. See "LCD Interface Pin Mapping" for summary.                                                            |

| FPDAT11     | O,<br>I/O | 23                                   | CN3  | Input           | <ul> <li>This pin has multiple functions.</li> <li>Panel Data bit 11 for TFT/D-TFD panels.</li> <li>General Purpose Input/Output pin GPIO4.</li> <li>Inverse Video select pin.</li> <li>This pin should be connected to IO V<sub>DD</sub> when unused. See "LCD Interface Pin Mapping" for summary.</li> </ul> |

| FPFRAME     | 0         | 39                                   | CN3  | 0               | Frame Pulse                                                                                                                                                                                                                                                                                                    |

| Pin Name | Туре | Pin # | Cell | RESET#<br>State                | Description                                                                                                                                                                 |

|----------|------|-------|------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPLINE   | 0    | 38    | CN3  | 0                              | Line Pulse                                                                                                                                                                  |

| FPSHIFT  | 0    | 28    | CN3  | 0                              | Shift Clock                                                                                                                                                                 |

| LCDPWR   | 0    | 43    | CO1  | 0 if CNF4 = 1<br>1 if CNF4 = 0 |                                                                                                                                                                             |

| DRDY     | 0    | 42    | CN3  | 0                              | This pin has multiple functions.  TFT/D-TFD Display Enable (DRDY).  LCD Backplane Bias (MOD).  Second Shift Clock (FPSHIFT2).  See "LCD Interface Pin Mapping" for summary. |

## 5.2.3 Clock Input

| Pin Name | Туре | Pin # | Driver | Description |

|----------|------|-------|--------|-------------|

| CLKI     | I    | 51    | С      | Input Clock |

### 5.2.4 Miscellaneous

| Pin Name | Туре      | Pin #                 | Cell       | RESET#<br>State    | Description                                                                                                                                                      |

|----------|-----------|-----------------------|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNF[4:0] | I         | 45, 46, 47,<br>48, 49 | С          | As set by hardware | These inputs are used to configure the S1D13704 - see "Summary of Configuration Options".  Must be connected directly to IO V <sub>DD</sub> or V <sub>SS</sub> . |

| GPIO0    | I/O,<br>I | 22                    | CS/<br>TS1 | Input              | This pin has multiple functions - see REG[03h] bit 2.  • General Purpose Input/Output pin.  • Hardware Power Save.                                               |

| TESTEN   | I         | 44                    | CD         | High<br>Impedance  | Test Enable input. This input must be connected to V <sub>SS</sub> .                                                                                             |

## 5.2.5 Power Supply

| Pin Name | Type | Pin#                             | Driver | Description            |

|----------|------|----------------------------------|--------|------------------------|

| COREVDD  | Р    | 1, 21, 41,<br>61                 | Р      | Core V <sub>DD</sub>   |

| IOVDD    | Р    | 10, 29, 52                       | Р      | IO V <sub>DD</sub>     |

| VSS      | Р    | 20, 27, 40,<br>50, 60, 72,<br>80 | Р      | Common V <sub>SS</sub> |

# **5.3 Summary of Configuration Options**

Table 5-1: Summary of Power On/Reset Options

| Configuration | Power On/Reset State |           |          |     |                                 |  |

|---------------|----------------------|-----------|----------|-----|---------------------------------|--|

| Pin           |                      | 1         |          |     | 0                               |  |

| CNF4          | Active high (On) LO  | DPWR p    | oolarity |     | Active low (On) LCDPWR polarity |  |

| CNF3          | Big Endian           |           |          |     | Little Endian                   |  |

|               | Select host bus into | erface as | follows: |     |                                 |  |

|               | CNF2                 | CNF1      | CNF0     | BS# | Host Bus                        |  |

|               | 0                    | 0         | 0        | Χ   | SH-4 interface                  |  |

|               | 0                    | 0         | 1        | Χ   | SH-3 interface                  |  |

|               | 0                    | 1         | 0        | Χ   | reserved                        |  |

| CNF[2:0]      | 0                    | 1         | 1        | Χ   | MC68K #1, 16-bit                |  |

| 0[=.0]        | 1                    | 0         | 0        | Χ   | reserved                        |  |

|               | 1                    | 0         | 1        | Χ   | MC68K #2, 16-bit                |  |

|               | 1                    | 1         | 0        | 0   | reserved                        |  |

|               | 1                    | 1         | 0        | 1   | reserved                        |  |

|               | 1                    | 1         | 1        | 0   | Generic #1, 16-bit              |  |

|               | 1                    | 1         | 1        | 1   | Generic #2, 16-bit              |  |

# 5.4 Host Bus Interface Pin Mapping

Table 5-2: Host Bus Interface Pin Mapping

| S1D13704<br>Pin Names | SH-3    | SH-4    | MC68K #1                      | MC68K #2        | Generic #1                 | Generic #2                    |

|-----------------------|---------|---------|-------------------------------|-----------------|----------------------------|-------------------------------|

| AB[15:1]              | A[15:1] | A[15:1] | A[15:1]                       | A[15:1]         | A[15:1]                    | A[15:1]                       |

| AB0                   | Α0      | A0      | LDS#                          | A0              | A0                         | A0                            |

| DB[15:0]              | D[15:0] | D[15:0] | D[15:0]                       | D[31:16]        | D[15:0]                    | D[15:0]                       |

| WE1#                  | WE1#    | WE1#    | UDS#                          | DS#             | WE1#                       | BHE#                          |

| CS#                   | CSn#    | CSn#    | External Decode               | External Decode | External Decode            | External Decode               |

| BCLK                  | CKIO    | CKIO    | CLK                           | CLK             | BCLK                       | BCLK                          |

| BS#                   | BS#     | BS#     | AS#                           | AS#             | connect to V <sub>SS</sub> | connect to IO V <sub>DD</sub> |

| RD/WR#                | RD/WR#  | RD/WR#  | R/W#                          | R/W#            | RD1#                       | connect to IO V <sub>DD</sub> |

| RD#                   | RD#     | RD#     | connect to IO V <sub>DD</sub> | SIZ1            | RD0#                       | RD#                           |

| WE0#                  | WE0#    | WE0#    | connect to IO V <sub>DD</sub> | SIZ0            | WE0#                       | WE#                           |

| WAIT#                 | WAIT#   | RDY#    | DTACK#                        | DSACK1#         | WAIT#                      | WAIT#                         |

| RESET#                | RESET#  | RESET#  | RESET#                        | RESET#          | RESET#                     | RESET#                        |

# 5.5 LCD Interface Pin Mapping

Table 5-3: LCD Interface Pin Mapping

|                      | Monochrome Passive Panel     |                              |                              | Color Passive Panel          |                              |                              |                              | Color TFT/D-TFD |        |

|----------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|-----------------|--------|

| S1D13704<br>Pin Name | 4-bit<br>Single              | 8-bit<br>Single              | 8-bit Dual                   | 4-bit<br>Single              | 8-bit<br>Single<br>Format 1  | 8-bit<br>Single<br>Format 2  | 8-bit Dual                   | 9-bit           | 12-bit |

| FPFRAME              |                              | FPFRAME                      |                              |                              |                              |                              |                              |                 |        |

| FPLINE               |                              |                              |                              |                              | FPLINE                       |                              |                              |                 |        |

| FPSHIFT              |                              |                              |                              |                              | FPSHIFT                      |                              |                              |                 |        |

| DRDY                 | MOD                          | MOD                          | MOD                          | MOD                          | FPSHIFT2                     | MOD                          | MOD                          | DR              | DY     |

| FPDAT0               | driven 0                     | D0                           | LD0                          | driven 0                     | D0                           | D0                           | LD0                          | R2              | R3     |

| FPDAT1               | driven 0                     | D1                           | LD1                          | driven 0                     | D1                           | D1                           | LD1                          | R1              | R2     |

| FPDAT2               | driven 0                     | D2                           | LD2                          | driven 0                     | D2                           | D2                           | LD2                          | R0              | R1     |

| FPDAT3               | driven 0                     | D3                           | LD3                          | driven 0                     | D3                           | D3                           | LD3                          | G2              | G3     |

| FPDAT4               | D0                           | D4                           | UD0                          | D0                           | D4                           | D4                           | UD0                          | G1              | G2     |

| FPDAT5               | D1                           | D5                           | UD1                          | D1                           | D5                           | D5                           | UD1                          | G0              | G1     |

| FPDAT6               | D2                           | D6                           | UD2                          | D2                           | D6                           | D6                           | UD2                          | B2              | В3     |

| FPDAT7               | D3                           | D7                           | UD3                          | D3                           | D7                           | D7                           | UD3                          | B1              | B2     |

| FPDAT8               | GPIO1                        | B0              | B1     |

| FPDAT9               | GPIO2                        | GPIO2           | R0     |

| FPDAT10              | GPIO3                        | GPIO3           | G0     |

| FPDAT11              | GPIO4/<br>HW Video<br>Invert | GPIO4           | В0     |

### Note

- Unused GPIO pins must be connected to IO V<sub>DD</sub>.

Hardware Video Invert is enabled on FPDAT11 by REG[02h] bit 1.

# 6 D.C. Characteristics

Table 6-1: Absolute Maximum Ratings

| Symbol               | Parameter               | Rating                                            | Units |

|----------------------|-------------------------|---------------------------------------------------|-------|

| Core V <sub>DD</sub> | Supply Voltage          | V <sub>SS</sub> - 0.3 to 4.6                      | V     |

| IO V <sub>DD</sub>   | Supply Voltage          | V <sub>SS</sub> - 0.3 to 6.0                      | V     |

| V <sub>IN</sub>      | Input Voltage           | V <sub>SS</sub> - 0.3 to IO V <sub>DD</sub> + 0.5 | V     |

| V <sub>OUT</sub>     | Output Voltage          | V <sub>SS</sub> - 0.3 to IO V <sub>DD</sub> + 0.5 | V     |

| T <sub>STG</sub>     | Storage Temperature     | -65 to 150                                        | ° C   |

| T <sub>SOL</sub>     | Solder Temperature/Time | 260 for 10 sec. max at lead                       | ° C   |

Table 6-2: Recommended Operating Conditions

| Symbol               | Parameter             | Condition             | Min      | Тур     | Max                | Units |

|----------------------|-----------------------|-----------------------|----------|---------|--------------------|-------|

| Core V <sub>DD</sub> | Supply Voltage        | V <sub>SS</sub> = 0 V | 3.0      | 3.3     | 3.6                | V     |

| IO V <sub>DD</sub>   | Supply Voltage        | V <sub>SS</sub> = 0 V | 3.0      | 3.3/5.0 | 5.5                | V     |

| V <sub>IN</sub>      | Input Voltage         |                       | $V_{SS}$ |         | IO V <sub>DD</sub> | V     |

| T <sub>OPR</sub>     | Operating Temperature |                       | -40      | 25      | 85                 | ° C   |

Table 6-3: Input Specifications

| Symbol           | Parameter                                    | Condition                                          | Min        | Тур | Max        | Units  |

|------------------|----------------------------------------------|----------------------------------------------------|------------|-----|------------|--------|

| V <sub>IL</sub>  | Low Level Input Voltage<br>CMOS inputs       | IO V <sub>DD</sub> = 3.3<br>5.0                    |            |     | 0.8<br>1.0 | V<br>V |

| V <sub>IH</sub>  | High Level Input Voltage<br>CMOS inputs      | IO V <sub>DD</sub> = 3.3<br>5.0                    | 2.0<br>3.5 |     |            | V<br>V |

| V <sub>T+</sub>  | Positive-going Threshold CMOS Schmitt inputs | IO V <sub>DD</sub> = 3.3<br>5.0                    | 1.1<br>2.0 |     | 2.4<br>4.0 | V      |

| V <sub>T-</sub>  | Negative-going Threshold CMOS Schmitt inputs | IO V <sub>DD</sub> = 3.3<br>5.0                    | 0.6<br>0.8 |     | 1.8<br>3.1 | V<br>V |

| I <sub>IZ</sub>  | Input Leakage Current                        | $V_{DD} = Max$ $V_{IH} = V_{DD}$ $V_{IL} = V_{SS}$ | -1         |     | 1          | μΑ     |

| C <sub>IN</sub>  | Input Pin Capacitance                        |                                                    |            |     | 10         | pF     |

| HR <sub>PD</sub> | Pull Down Resistance                         | $V_I = V_{DD}$                                     | 50         | 100 | 300        | kΩ     |

Table 6-4: Output Specifications

| Symbol           | Parameter                                                                               | Condition                                                                       | Min                      | Тур | Max | Units |

|------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------|-----|-----|-------|

| V <sub>OL</sub>  | Low Level Output Voltage<br>Type 1 - TS1, CO1<br>Type 2- TS2, CO2<br>Type 3 - TS3, CO3  | $I_{OL} = 3mA$ $I_{OL} = 6mA$ $I_{OL} = 12mA$                                   |                          |     | 0.4 | V     |

| V <sub>OH</sub>  | High Level Output Voltage<br>Type 1 - TS1, CO1<br>Type 2- TS2, CO2<br>Type 3 - TS3, CO3 | I <sub>OL</sub> = -1.5 mA<br>I <sub>OL</sub> = -3 mA<br>I <sub>OL</sub> = -6 mA | IO V <sub>DD</sub> - 0.4 |     |     | V     |

| l <sub>OZ</sub>  | Output Leakage Current                                                                  | $V_{DD} = MAX$ $V_{OH} = V_{DD}$ $V_{OL} = V_{SS}$                              | -1                       |     | 1   | μΑ    |

| C <sub>OUT</sub> | Output Pin Capacitance                                                                  |                                                                                 |                          |     | 10  | pF    |

| C <sub>BID</sub> | Bidirectional Pin Capacitance                                                           |                                                                                 |                          |     | 10  | pF    |

## 7 A.C. Characteristics

Conditions: IO  $V_{DD}$  = 3.3V  $\pm$  10% or IO  $V_{DD}$  = 5V  $\pm$  10%  $T_A$  = -40° C to 85° C  $T_{rise}$  and  $T_{fall}$  for all inputs must be  $\leq$  5 nsec (10%  $\sim$  90%)  $C_L$  = 60pF (Bus/MPU Interface)  $C_L$  = 60pF (LCD Panel Interface)

### 7.1 Bus Interface Timing

### 7.1.1 SH-4 Interface Timing

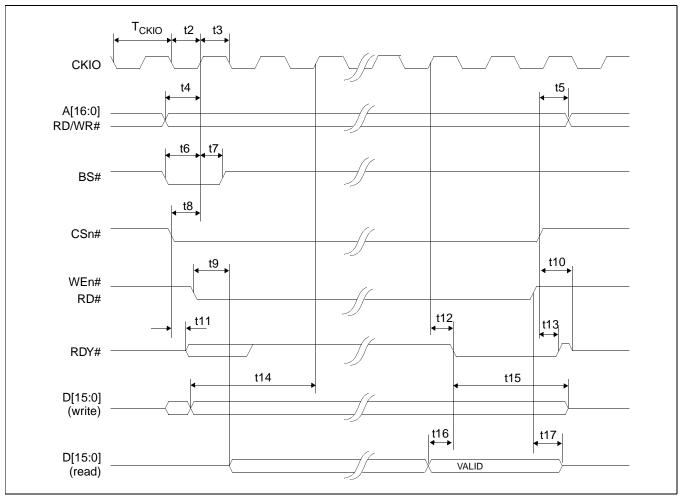

Figure 7-1: SH-4 Timing

### Note

The SH-4 Wait State Control Register for the area in which the S1D13704 resides must be set to a non-zero value. The SH-4 read-to-write cycle transition must be set to a non-zero value (with reference to BUSCLK).

Table 7-1: SH-4 Timing

| Symbol            | Parameter                                                      | Min                 | Max | Units |

|-------------------|----------------------------------------------------------------|---------------------|-----|-------|

| f <sub>CKIO</sub> | Bus Clock frequency                                            | 0                   | 50  | MHz   |

| T <sub>CKIO</sub> | Bus Clock period                                               | 1/f <sub>CKIO</sub> |     |       |

| t2                | Clock pulse width high                                         | 17                  |     | ns    |

| t3                | Clock pulse width low                                          | 16                  |     | ns    |

| t4                | A[15:0], RD/WR# setup to CKIO                                  | 0                   |     | ns    |

| t5                | A[15:0], RD/WR# hold from CS#                                  | 0                   |     | ns    |

| t6                | BS# setup                                                      | 5                   |     | ns    |

| t7                | BS# hold                                                       | 5                   |     | ns    |

| t8                | CSn# setup                                                     | 0                   |     | ns    |

| t9                | Falling edge RD# to DB[15:0] driven                            |                     | 25  | ns    |

| t10               | Rising edge CSn# to RDY# high impedance                        |                     | t1  | ns    |

| t11               | Falling edge CSn# to RDY# driven                               |                     | 20  | ns    |

| t12               | CKIO to RDY# low                                               |                     | 20  | ns    |

| t13               | Rising edge CSn# to RDY# high                                  |                     | 20  | ns    |

| t14               | DB[15:0] setup to 2 <sup>nd</sup> CKIO after BS# (write cycle) | 0                   |     | ns    |

| t15               | DB[15:0] hold (write cycle)                                    | 0                   |     | ns    |

| t16               | DB[15:0] valid to RDY# falling edge setup time (read cycle)    | 0                   |     | ns    |

| t17               | Rising edge RD# to DB[15:0] high impedance (read cycle)        |                     | 10  | ns    |

### Note

CKIO may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

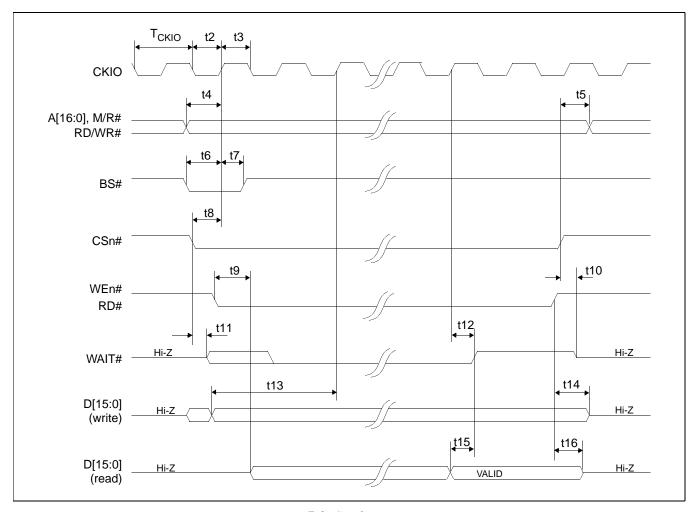

### 7.1.2 SH-3 Interface Timing

Figure 7-2: SH-3 Bus Timing

### Note

The SH-3 Wait State Control Register for the area in which the S1D13704 resides must be set to a non-zero value.

Table 7-2: SH-3 Bus Timing

| Symbol            | Parameter                                                      | Min                 | Max <sup>a</sup> | Units |

|-------------------|----------------------------------------------------------------|---------------------|------------------|-------|

| f <sub>CKIO</sub> | Bus Clock frequency                                            | 0                   | 50               | MHz   |

| T <sub>CKIO</sub> | Bus Clock period                                               | 1/f <sub>CKIO</sub> |                  |       |

| t2                | Clock pulse width high                                         | 17                  |                  | ns    |

| t3                | Clock pulse width low                                          | 16                  |                  | ns    |

| t4                | A[15:0], RD/WR# setup to CKIO                                  | 0                   |                  | ns    |

| t5                | A[15:0], RD/WR# hold from CS#                                  | 0                   |                  | ns    |

| t6                | BS# setup                                                      | 5                   |                  | ns    |

| t7                | BS# hold                                                       | 5                   |                  | ns    |

| t8                | CSn# setup                                                     | 0                   |                  | ns    |

| t9                | Falling edge RD# to DB[15:0] driven                            |                     | 25               | ns    |

| t10               | Rising edge CSn# to WAIT# high impedance                       |                     | 10               | ns    |

| t11               | Falling edge CSn# to WAIT# driven                              |                     | 15               | ns    |

| t12               | CKIO to WAIT# delay                                            |                     | 20               | ns    |

| t13               | DB[15:0] setup to 2 <sup>nd</sup> CKIO after BS# (write cycle) | 0                   |                  | ns    |

| t14               | DB[15:0] hold from rising edge of WEn# (write cycle)           | 0                   |                  | ns    |

| t15               | DB[15:0] valid to RDY# falling edge setup time (read cycle)    | 0                   |                  | ns    |

| t16               | Rising edge RD# to DB[15:0] high impedance (read cycle)        |                     | 10               | ns    |

<sup>&</sup>lt;sup>a</sup> One Software WAIT State Required

### Note

CKIO may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

#### $T_{CLK}$ CLK A[15:1] CS# R/W# VALID t2 t1 AS# UDS#, LDS# INVALID t6 t3 t5 Hi-Z Hi-Z DTACK# t8 t7 D[15:0] Hi-Z Hi-Z VALID (write t11 t10 D[15:0] Hi-Z (read) VALID

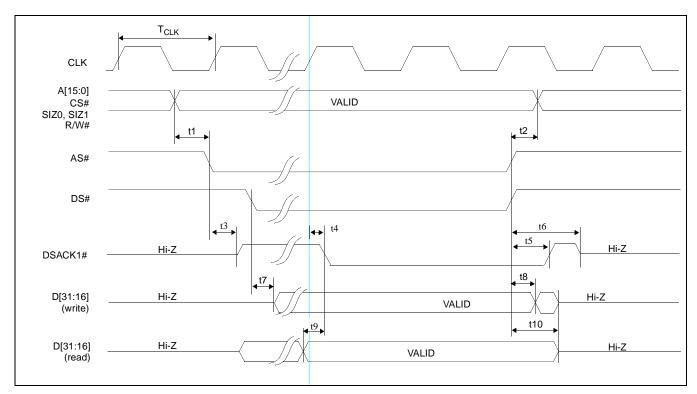

# 7.1.3 Motorola M68K #1 Interface Timing

Figure 7-3: M68K #1 Bus Timing (MC68000)

| Symbol           | Parameter                                              | Min                | Max              | Units |

|------------------|--------------------------------------------------------|--------------------|------------------|-------|

| f <sub>CLK</sub> | Bus Clock Frequency                                    | 0                  | 33               | MHz   |

| T <sub>CLK</sub> | Bus Clock period                                       | 1/f <sub>CLK</sub> |                  |       |

| t1               | A[15:1], CS# valid before AS# falling edge             | 0                  |                  | ns    |

| t2               | A[15:1], CS# hold from AS# rising edge                 | 0                  |                  | ns    |

| t3               | AS# low to DTACK# driven high                          |                    | 16               | ns    |

| t4               | CLK to DTACK# low                                      |                    | 15               | ns    |

| t5               | AS# high to DTACK# high                                |                    | 20               | ns    |

| t6               | AS# high to DTACK# high impedance                      |                    | T <sub>CLK</sub> |       |

| t7               | UDS#, LDS# falling edge to D[15:0] valid (write cycle) |                    | T <sub>CLK</sub> |       |

| t8               | D[15:0] hold from AS# rising edge (write cycle)        | 0                  |                  | ns    |

| t9               | UDS#, LDS# falling edge to D[15:0] driven (read cycle) |                    | 15               | ns    |

| t10              | D[15:0] valid to DTACK# falling edge (read cycle)      | 0                  |                  | ns    |

| t11              | UDS#, LDS# rising edge to D[15:0] high impedance       |                    | 10               | ns    |

Table 7-3: M68K #1 Bus Timing (MC68000)

#### Note

CLK may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

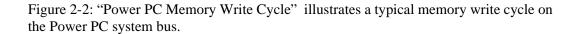

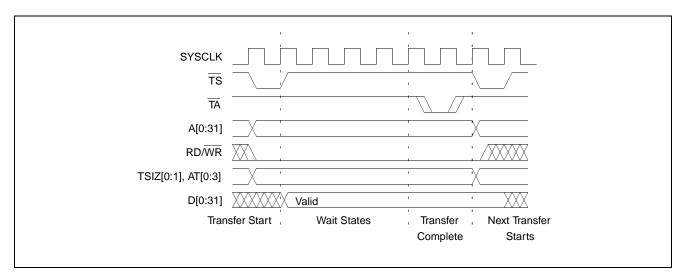

# 7.1.4 Motorola M68K #2 Interface Timing

Figure 7-4: M68K #2 Timing (MC68030)

Table 7-4: M68K #2 Timing (MC68030)

| Symbol           | Parameter                                               | Min                | Max                 | Units |

|------------------|---------------------------------------------------------|--------------------|---------------------|-------|

| f <sub>CLK</sub> | Bus Clock frequency                                     | 0                  | 33                  | MHz   |

| T <sub>CLK</sub> | Bus Clock period                                        | 1/f <sub>CLK</sub> |                     |       |

| t1               | A[15:0], CS#, SIZ0, SIZ1 valid before AS# falling edge  | 0                  |                     | ns    |

| t2               | A[15:0], CS#, SIZ0, SIZ1 hold from AS#, DS# rising edge | 0                  |                     | ns    |

| t3               | AS# low to DSACK1# driven high                          |                    | 22                  | ns    |

| t4               | CLK to DSACK1# low                                      |                    | 18                  | ns    |

| t5               | AS# high to DSACK1# high                                |                    | 26                  | ns    |

| t6               | AS# high to DSACK1# high impedance                      |                    | T <sub>CLK</sub>    |       |

| t7               | DS# falling edge to D[31:16] valid (write cycle)        |                    | T <sub>CLK</sub> /2 |       |

| t8               | AS#, DS# rising edge to D[31:16] invalid (write cycle)  | 0                  |                     | ns    |

| t9               | D[31:16] valid to DSACK1# low (read cycle)              | 0                  |                     | ns    |

| t10              | AS#, DS# rising edge to D[31:16] high impedance         |                    | 20                  | ns    |

#### Note

CLK may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

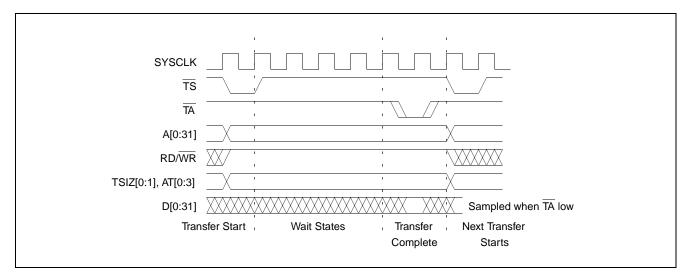

# 7.1.5 Generic #1 Interface Timing

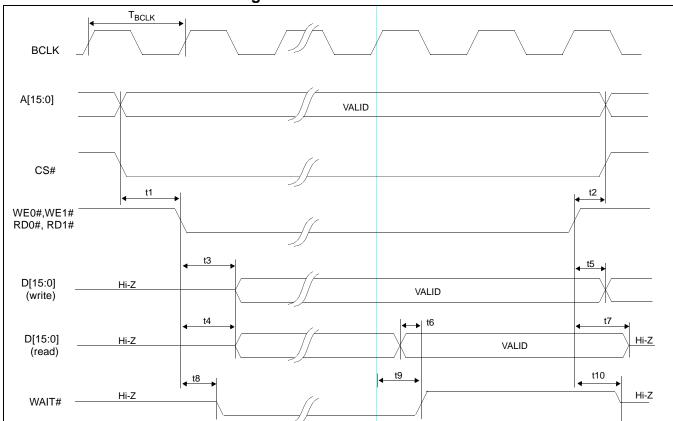

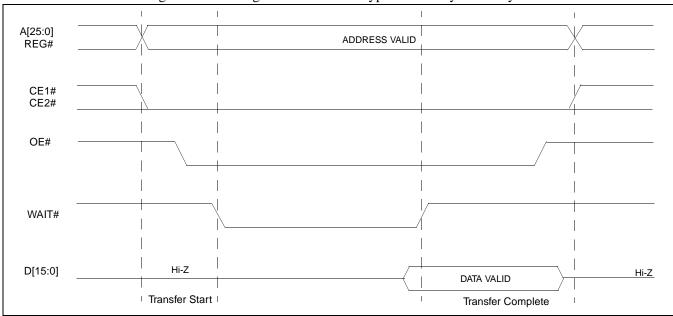

Figure 7-5: Generic #1 Timing

Table 7-5: Generic #1 Timing

| Symbol            | Parameter                                                                             | Min                 | Max               | Units |

|-------------------|---------------------------------------------------------------------------------------|---------------------|-------------------|-------|

| f <sub>BCLK</sub> | Bus Clock frequency                                                                   | 0                   | 50                | MHz   |

| T <sub>BCLK</sub> | Bus Clock period                                                                      | 1/f <sub>BCLK</sub> |                   | MHz   |

| t1                | A[15:0], CS# valid to WE0#, WE1# low (write cycle) or RD0#, RD1# low (read cycle)     | 0                   |                   | ns    |

| t2                | WE0#, WE1# high (write cycle) or RD0#, RD1# high (read cycle) to A[15:0], CS# invalid | 0                   |                   | ns    |

| t3                | WE0#, WE1# low to D[15:0] valid (write cycle)                                         |                     | T <sub>BCLK</sub> |       |

| t4                | RD0#, RD1# low to D[15:0] driven (read cycle)                                         |                     | 17                | ns    |

| t5                | WE0#, WE1# high to D[15:0] invalid (write cycle)                                      | 0                   |                   | ns    |

| t6                | D[15:0] valid to WAIT# high (read cycle)                                              | 0                   |                   | ns    |

| t7                | RD0#, RD1# high to D[15:0] high impedance (read cycle)                                |                     | 10                | ns    |

| t8                | WE0#, WE1# low (write cycle) or RD0#, RD1# low (read cycle) to WAIT# driven low       |                     | 16                | ns    |

| t9                | BCLK to WAIT# high                                                                    |                     | 16                | ns    |

| t10               | WE0#, WE1# high (write cycle) or RD0#, RD1# high (read cycle) to WAIT# high impedance |                     | 11                | ns    |

#### Note

BCLK may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

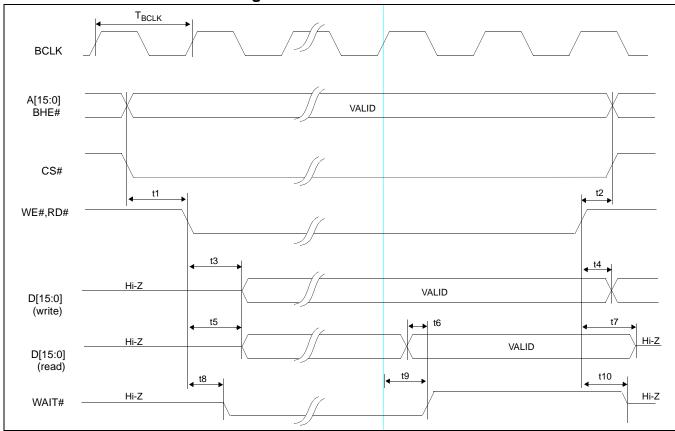

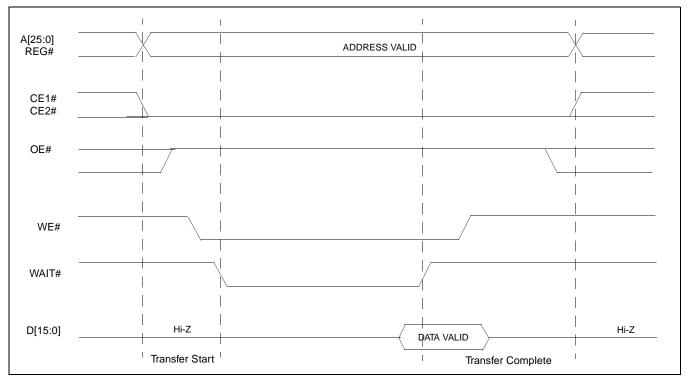

# 7.1.6 Generic #2 Interface Timing

Figure 7-6: Generic #2 Timing

Table 7-6: Generic #2 Timing

| Symbol            | Parameter                                       | Min                 | Max               | Units |

|-------------------|-------------------------------------------------|---------------------|-------------------|-------|

| f <sub>BCLK</sub> | Bus Clock frequency                             | 0                   | 50                | MHz   |

| T <sub>BCLK</sub> | Bus Clock period                                | 1/f <sub>BCLK</sub> |                   |       |

| t1                | A[15:0], BHE#, CS# valid to WE#, RD# low        | 0                   |                   | ns    |

| t2                | WE#, RD# high to A[15:0], BHE#, CS# invalid     | 0                   |                   | ns    |

| t3                | WE# low to D[15:0] valid (write cycle)          |                     | T <sub>BCLK</sub> |       |

| t4                | WE# high to D[15:0] invalid (write cycle)       | 0                   |                   | ns    |

| t5                | RD# low to D[15:0] driven (read cycle)          |                     | 16                | ns    |

| t6                | D[15:0] valid to WAIT# high (read cycle)        | 0                   |                   | ns    |

| t7                | RD# high to D[15:0] high impedance (read cycle) |                     | 10                | ns    |

| t8                | WE#, RD# low to WAIT# driven low                |                     | 14                | ns    |

| t9                | BCLK to WAIT# high                              |                     | 16                | ns    |

| t10               | WE#, RD# high to WAIT# high impedance           |                     | 11                | ns    |

### Note

BCLK may be turned off (held low) between accesses - see Section 13.5, "Turning Off BCLK Between Accesses" on page 86

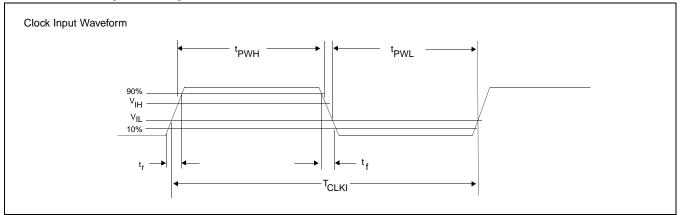

# 7.2 Clock Input Requirements

Figure 7-7: Clock Input Requirements

Table 7-7: Clock Input Requirements

| Symbol            | Parameter                           | Min                 | Max | Units |

|-------------------|-------------------------------------|---------------------|-----|-------|

| f <sub>CLKI</sub> | Input Clock Frequency (CLKI)        | 0                   | 50  | MHz   |

| T <sub>CLKI</sub> | Input Clock period (CLKI)           | 1/f <sub>CLKI</sub> |     |       |

| t <sub>PWH</sub>  | Input Clock Pulse Width High (CLKI) | 8                   |     | ns    |

| t <sub>PWL</sub>  | Input Clock Pulse Width Low (CLKI)  | 8                   |     | ns    |

| t <sub>f</sub>    | Input Clock Fall Time (10% - 90%)   |                     | 5   | ns    |

| t <sub>r</sub>    | Input Clock Rise Time (10% - 90%)   |                     | 5   | ns    |

### Note

When CLKI is > 25MHz it must be divided by 2 (REG[02h] bit 4 = 1).

# 7.3 Display Interface

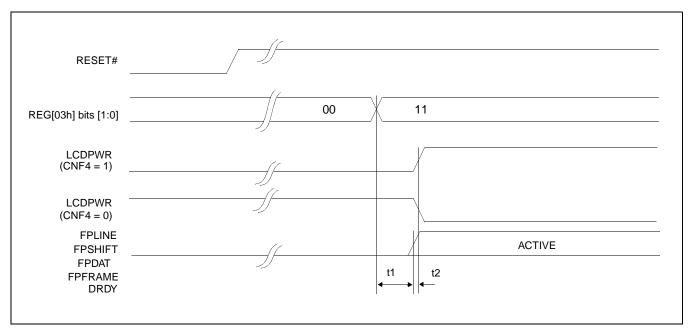

# 7.3.1 Power On/Reset Timing

Figure 7-8: LCD Panel Power On/Reset Timing

| Symbol | Parameter                                                | Min | Тур | Max                  | Units  |

|--------|----------------------------------------------------------|-----|-----|----------------------|--------|

| t1     | REG[03h] to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY active |     |     | T <sub>FPFRAME</sub> | ns     |

| t2     | FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY active to LCDPWR   |     | 0   |                      | Frames |

#### Note

Where  $T_{\mbox{FPFRAME}}$  is the period of FPFRAME and  $T_{\mbox{PCLK}}$  is the period of the pixel clock.

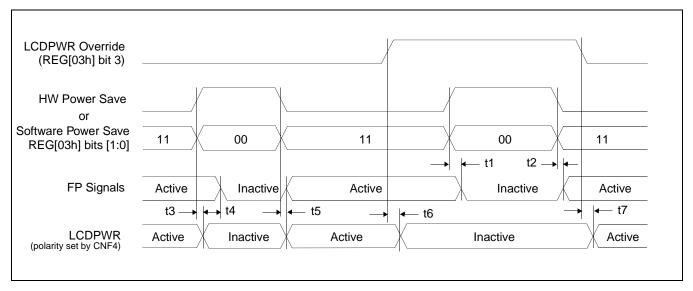

# 7.3.2 Power Down/Up Timing

Figure 7-9: Power Down/Up Timing

Table 7-8: Power Down/Up Timing

| Symbol | Parameter                                                                                            | Min | Тур | Max | Units |

|--------|------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t1     | HW Power Save active to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY inactive - LCDPWR Override = 1         |     |     | 1   | Frame |

| t2     | HW Power Save inactive to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY active - LCDPWR Override = 1         |     |     | 1   | Frame |

| t3     | HW Power Save active to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY inactive - LCDPWR Override = 0         |     |     | 1   | Frame |

| t4     | LCDPWR low to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY inactive - LCDPWR Override = 0                   |     | 127 |     | Frame |

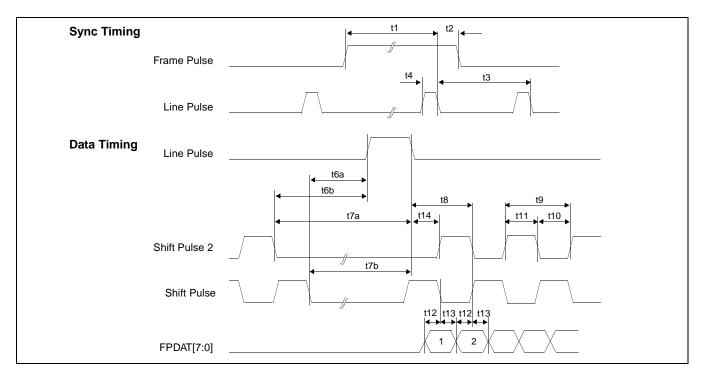

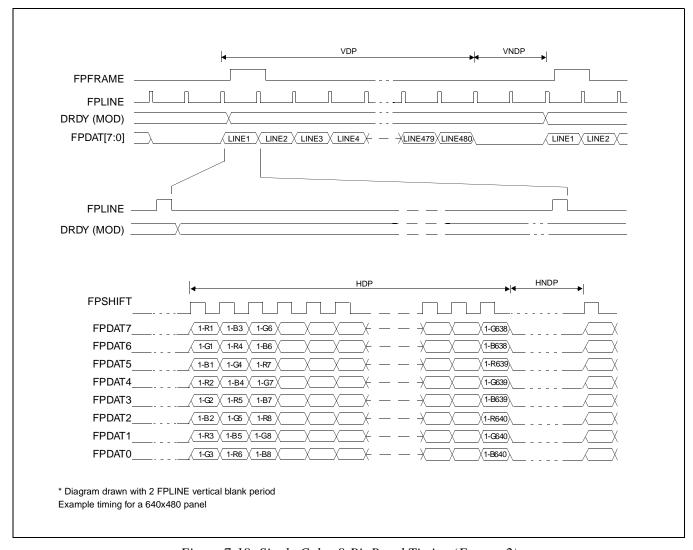

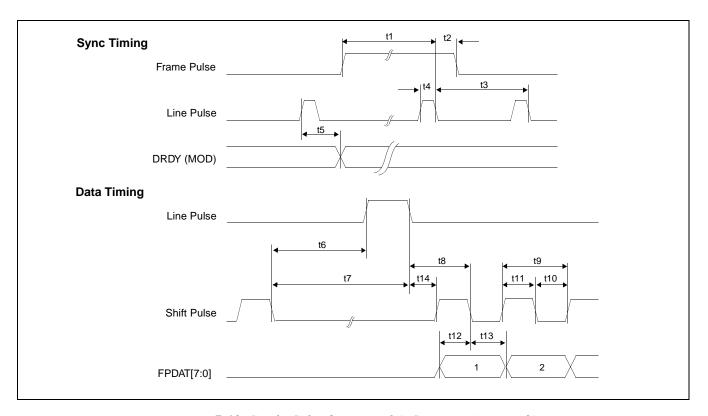

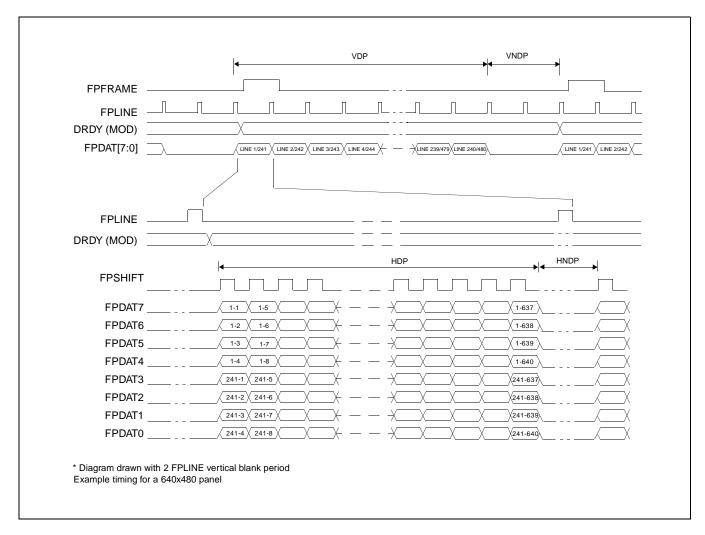

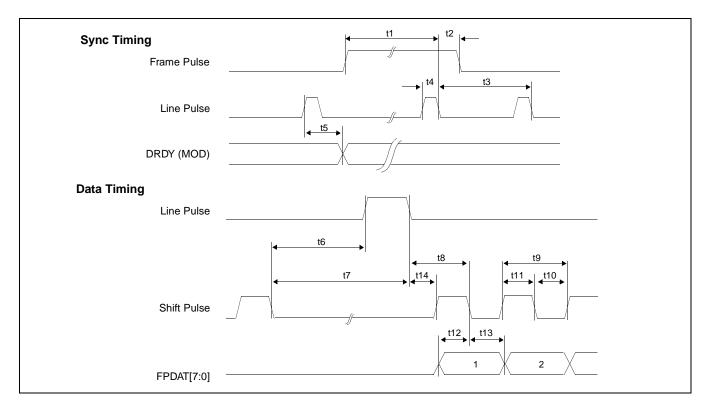

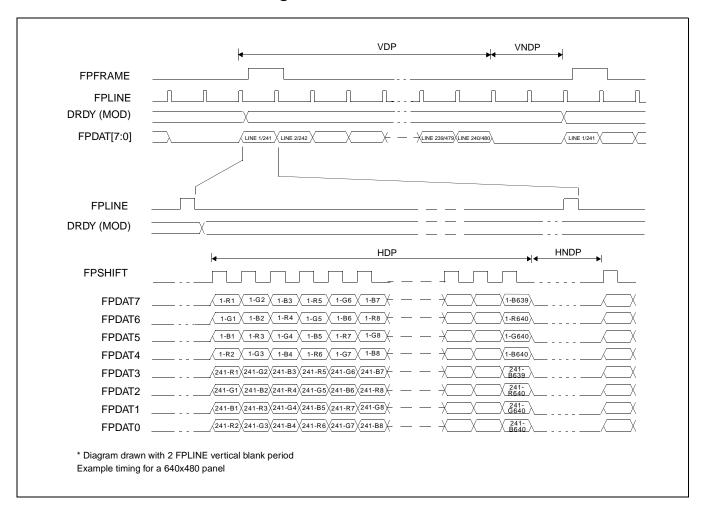

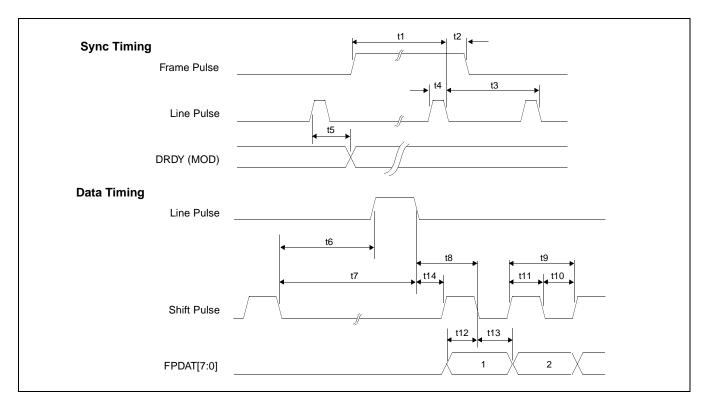

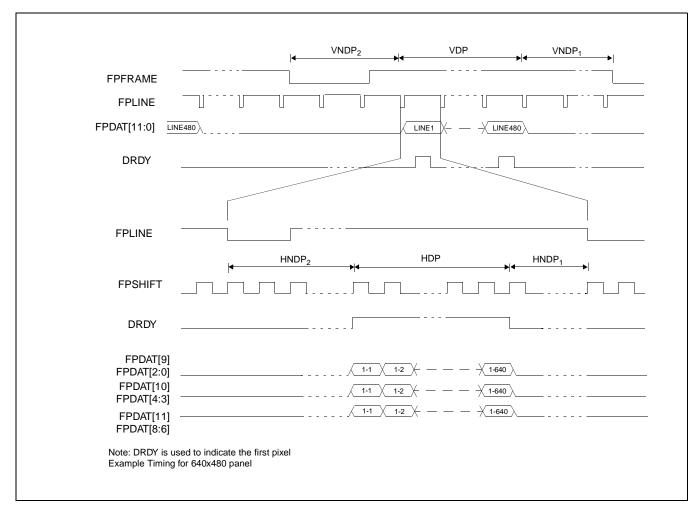

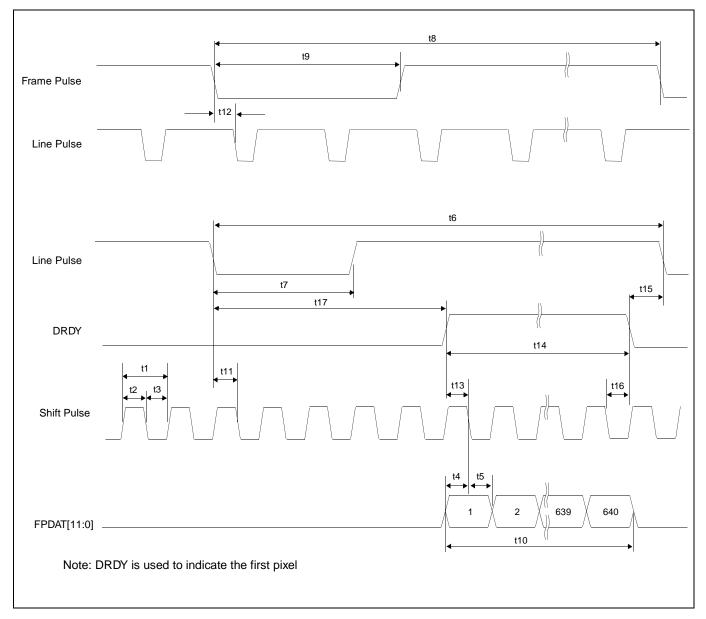

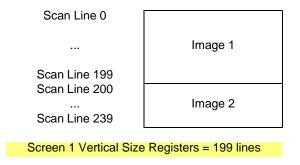

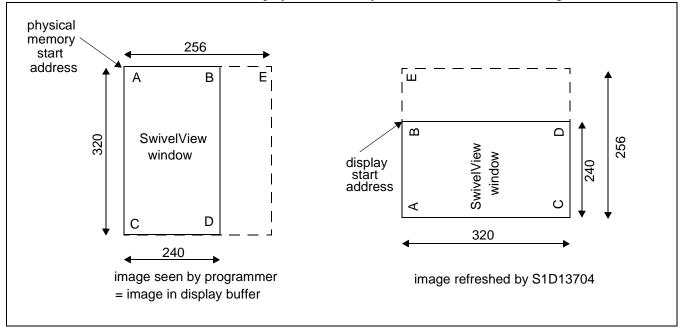

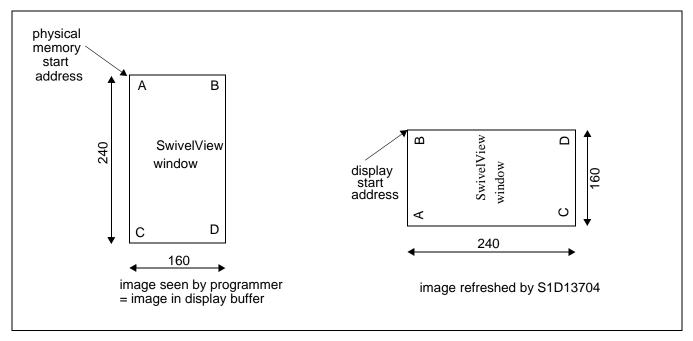

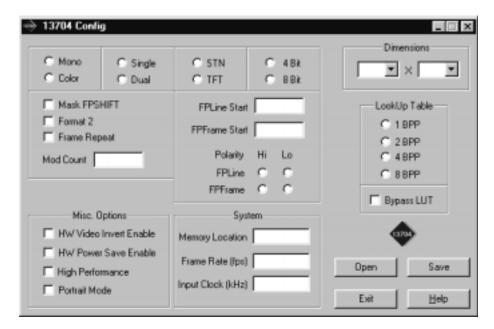

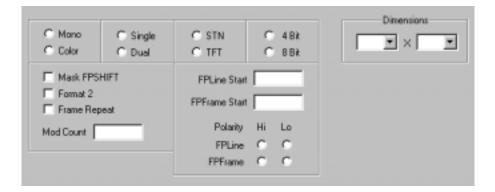

| t5     | HW Power Save inactive to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY, LCDPWR active - LCDPWR Override = 0 |     | 0   |     | Frame |