## GateMate<sup>™</sup> FPGA Datasheet

# CCGM1A1

#### Copyright 2019 - 2023 Cologne Chip AG

#### All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights. Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

## Contents

| Ab | About this Document |          |                                                          | 13 |

|----|---------------------|----------|----------------------------------------------------------|----|

| 1  | Intro               | oductio  | n                                                        | 17 |

|    | 1.1                 | Introdu  | uction                                                   | 17 |

|    | 1.2                 | Featur   | es                                                       | 18 |

| 2  | Arch                | nitectur | e                                                        | 21 |

|    | 2.1                 | GateM    | late (TM) FPGA Overview                                  | 21 |

|    | 2.2                 | Cologr   | ne Programmable Element (CPE)                            | 22 |

|    | 2.3                 | Genera   | al purpose input / output (GPIO) ....................... | 24 |

|    | 2.4                 | Embeo    | dded Block RAM                                           | 27 |

|    |                     | 2.4.1    | Block RAM Overview                                       | 27 |

|    |                     | 2.4.2    | Block RAM Architecture                                   | 28 |

|    |                     | 2.4.3    | TDP Mode                                                 | 30 |

|    |                     | 2.4.4    | SDP Mode                                                 | 31 |

|    |                     | 2.4.5    | Expanding Data Widths and Cascade Mode                   | 33 |

|    |                     | 2.4.6    | Memory Mapping and Content Initialization                | 33 |

|    |                     | 2.4.7    | ECC Encoding / Decoding                                  | 34 |

|    |                     | 2.4.8    | RAM Access Modes and Enable                              | 36 |

|    |                     | 2.4.9    | FIFO Application                                         | 37 |

|    | 2.5                 | Clock    | Generators (PLL)                                         | 45 |

|   | 2.6               | Global                                                                                                         | Global Mesh Architecture    46                                                                                                                                                            |                                                                                                                                                                                    |  |

|---|-------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |                   | 2.6.1                                                                                                          | Overview of the Global Mesh Signal Injection                                                                                                                                              | 46                                                                                                                                                                                 |  |

|   |                   | 2.6.2                                                                                                          | Clock Input Multiplexers CLKIN                                                                                                                                                            | 46                                                                                                                                                                                 |  |

|   |                   | 2.6.3                                                                                                          | PLL Wrapper                                                                                                                                                                               | 46                                                                                                                                                                                 |  |

|   |                   | 2.6.4                                                                                                          | GLBOUT Multiplexers                                                                                                                                                                       | 49                                                                                                                                                                                 |  |

|   |                   | 2.6.5                                                                                                          | Use of the CC_BUFG Elements in HDL Design Sources                                                                                                                                         | 51                                                                                                                                                                                 |  |

|   | 2.7               | Clocki                                                                                                         | ng Schemes                                                                                                                                                                                | 52                                                                                                                                                                                 |  |

|   |                   | 2.7.1                                                                                                          | The Methods of Clock Distribution                                                                                                                                                         | 52                                                                                                                                                                                 |  |

|   |                   | 2.7.2                                                                                                          | Clock Distribution via the Routing Structure                                                                                                                                              | 56                                                                                                                                                                                 |  |

|   |                   | 2.7.3                                                                                                          | Clock Distribution via the Global Mesh                                                                                                                                                    | 56                                                                                                                                                                                 |  |

|   |                   | 2.7.4                                                                                                          | Clock Distribution via CPLs                                                                                                                                                               | 56                                                                                                                                                                                 |  |

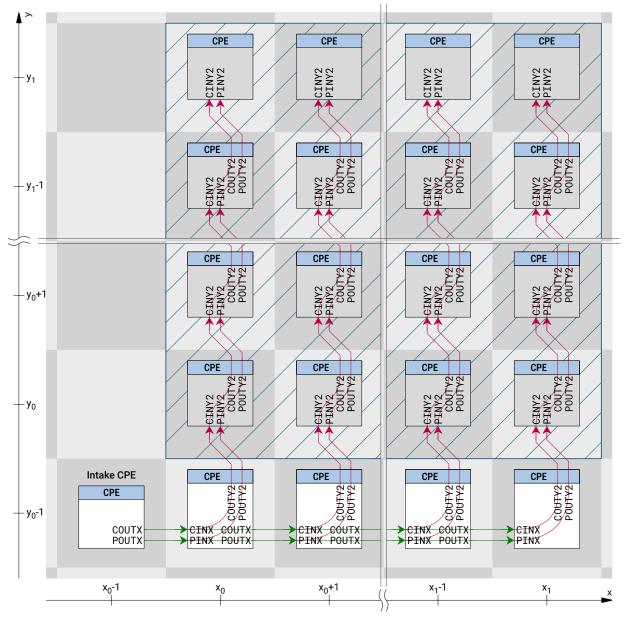

|   |                   |                                                                                                                | 2.7.4.1 Intake CPE with chained CPE row                                                                                                                                                   | 58                                                                                                                                                                                 |  |

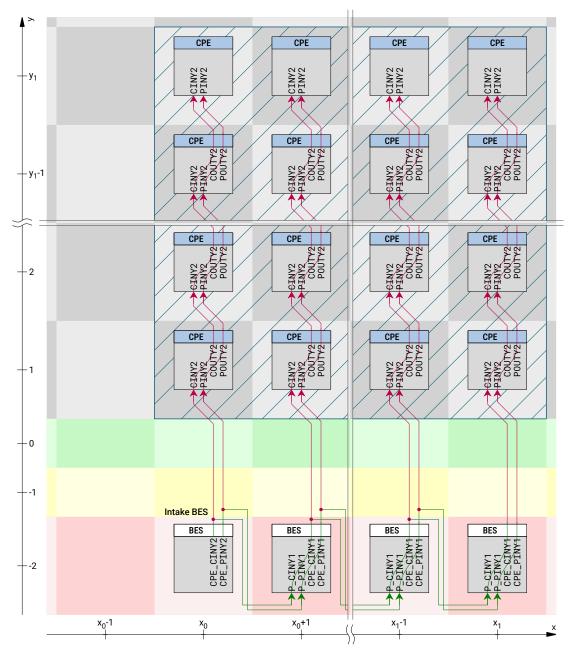

|   |                   |                                                                                                                | 2.7.4.2 Intake BES with chained BES row                                                                                                                                                   | 59                                                                                                                                                                                 |  |

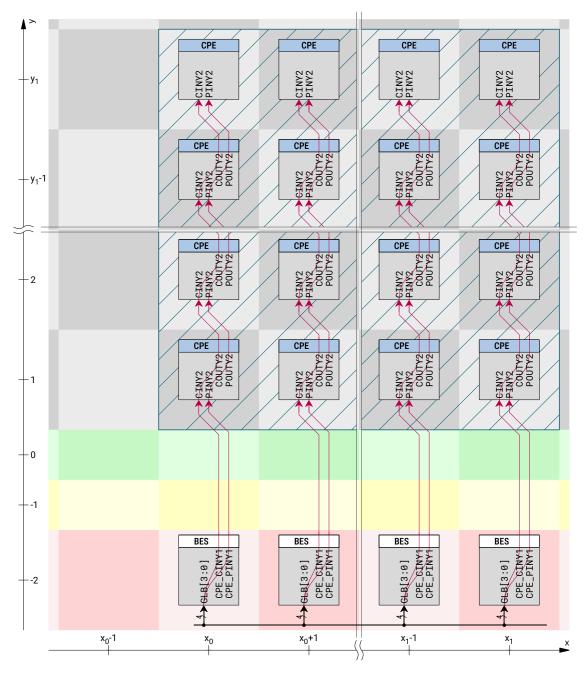

|   |                   |                                                                                                                | 2.7.4.3 Unchained BES row with Global Mesh pick-up                                                                                                                                        | 60                                                                                                                                                                                 |  |

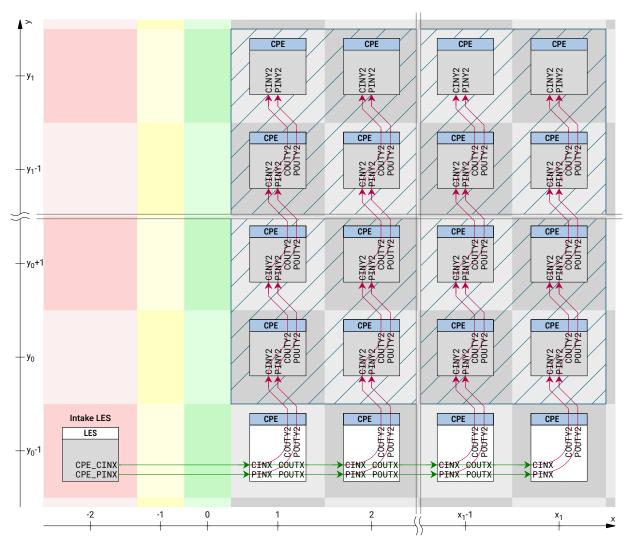

|   |                   |                                                                                                                | 2.7.4.4 Intake LES with chained CPE row                                                                                                                                                   | 61                                                                                                                                                                                 |  |

|   | 2.8               | Routin                                                                                                         | g Structure                                                                                                                                                                               | 62                                                                                                                                                                                 |  |

|   | 2.9               | Power                                                                                                          | Supply                                                                                                                                                                                    | 64                                                                                                                                                                                 |  |

|   |                   |                                                                                                                |                                                                                                                                                                                           |                                                                                                                                                                                    |  |

| 3 | Wor               | kflow aı                                                                                                       | nd Hardware Setup                                                                                                                                                                         | 65                                                                                                                                                                                 |  |

| 3 | <b>Wor</b><br>3.1 |                                                                                                                | nd Hardware Setup<br>Workflow                                                                                                                                                             | <b>65</b><br>65                                                                                                                                                                    |  |

| 3 |                   |                                                                                                                | Workflow                                                                                                                                                                                  | 65                                                                                                                                                                                 |  |

| 3 |                   | FPGA                                                                                                           | Workflow                                                                                                                                                                                  | 65<br>65                                                                                                                                                                           |  |

| 3 |                   | FPGA<br>3.1.1<br>3.1.2                                                                                         | Workflow                                                                                                                                                                                  | 65<br>65<br>67                                                                                                                                                                     |  |

| 3 |                   | FPGA<br>3.1.1<br>3.1.2                                                                                         | Workflow       .         Overview       .         Synthesis       .         Implementation       .                                                                                        | 65<br>65<br>67<br>68                                                                                                                                                               |  |

| 3 |                   | FPGA<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                       | Workflow                                                                                                                                                                                  | 65<br>65<br>67<br>68<br>71                                                                                                                                                         |  |

| 3 | 3.1               | FPGA<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                                                                       | Workflow       .         Overview       .         Synthesis       .         Implementation       .         Configuration       .                                                          | 65<br>65<br>67<br>68<br>71<br>74                                                                                                                                                   |  |

| 3 | 3.1               | FPGA<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw                                                              | Workflow       .         Overview       .         Synthesis       .         Implementation       .         Configuration       .         are Setup       .                                | <ul> <li>65</li> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> </ul>                                                                                     |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1                                                        | Workflow       .         Overview       .         Synthesis       .         Implementation       .         Configuration       .         are Setup       .         Power-on Reset       . | <ul> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> <li>75</li> </ul>                                                                                     |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1<br>3.2.2<br>3.2.3                                      | Workflow                                                                                                                                                                                  | 65<br>65<br>67<br>68<br>71<br>74<br>74<br>74<br>75<br>76                                                                                                                           |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1<br>3.2.2<br>3.2.3                                      | Workflow                                                                                                                                                                                  | <ul> <li>65</li> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>78</li> </ul>                                     |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1<br>3.2.2<br>3.2.3<br>Config                            | Workflow                                                                                                                                                                                  | <ul> <li>65</li> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> </ul>                                     |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1<br>3.2.2<br>3.2.3<br>Config<br>3.3.1                   | Workflow                                                                                                                                                                                  | <ul> <li>65</li> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>79</li> </ul>             |  |

| 3 | 3.1               | FPGA 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>Hardw<br>3.2.1<br>3.2.2<br>3.2.3<br>Config<br>3.3.1<br>3.3.2<br>3.3.3 | Workflow                                                                                                                                                                                  | <ul> <li>65</li> <li>65</li> <li>67</li> <li>68</li> <li>71</li> <li>74</li> <li>74</li> <li>74</li> <li>75</li> <li>76</li> <li>78</li> <li>78</li> <li>79</li> <li>80</li> </ul> |  |

| Contents _ |

|------------|

|------------|

| 6 | 5.1<br>5.2 | CCGM     | I1A1 324-Ball FBGA Pinout |    |

|---|------------|----------|---------------------------|----|

|   | 0.1        |          |                           |    |

|   | 5.1        | CCGM     | 1A1 324-Ball FBGA Pinout  | 99 |

|   |            |          |                           |    |

| 5 | Pino       | ut       |                           | 99 |

| 4 | Elec       | trical C | haracteristics            | 93 |

|   |            | 3.4.7    | Boundary-Scan Test        | 90 |

|   |            | 3.4.6    | Access to SPI data flash  | 88 |

|   |            | 3.4.5    | Access to SPI Bus         | 86 |

|   |            | 3.4.4    | JTAG Configuration        | 85 |

|   |            | 3.4.3    | Common JTAG Instructions  | 84 |

|   |            | ••••     | JTAG Usage                | 84 |

# **List of Figures**

| 2.1  | Simplified architecture overview                                                                     | 21 |

|------|------------------------------------------------------------------------------------------------------|----|

| 2.2  | Cologne Programmable Element (CPE)                                                                   | 22 |

| 2.3  | GPIO cell in single-ended mode                                                                       | 24 |

| 2.4  | GPIO cell in LVDS mode                                                                               | 25 |

| 2.5  | GPIO bank                                                                                            | 26 |

| 2.6  | Block RAM arrangement                                                                                | 27 |

| 2.7  | High level block diagram of a block RAM cell                                                         | 29 |

| 2.8  | Internal data flow of DPSRAM in TDP 20K mode                                                         | 31 |

| 2.9  | Internal data flow of DPSRAM in TDP 40K mode                                                         | 31 |

| 2.10 | Internal data flow of DPSRAM in SDP 20K mode                                                         | 32 |

| 2.11 | Internal data flow of DPSRAM in SDP 40K mode                                                         | 32 |

| 2.12 | Structure of two adjacent DPSRAMs forming one $64K \times 1$ bit memory via cascade feature $\ldots$ | 34 |

| 2.13 | Logical data mapping of memory at physical address 0                                                 | 35 |

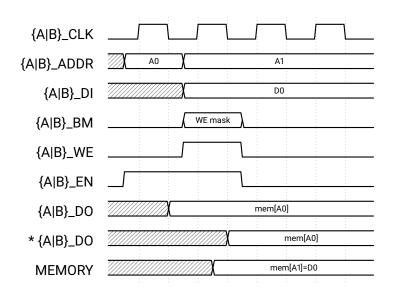

| 2.14 | Timing diagram of a single read access                                                               | 37 |

| 2.15 | Timing diagram of a NO CHANGE access                                                                 | 37 |

| 2.16 | Timing diagram of a WRITE THROUGH access                                                             | 38 |

| 2.17 | Internal data flow of DPSRAM in FIFO mode                                                            | 38 |

| 2.18 | Writing to an empty synchronous FIFO                                                                 | 40 |

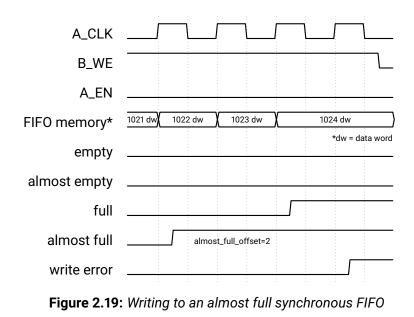

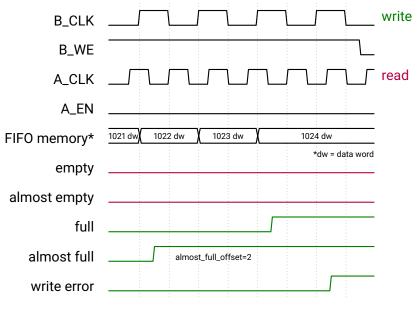

| 2.19 | Writing to an almost full synchronous FIFO                                                           | 41 |

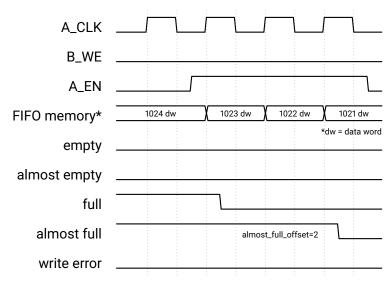

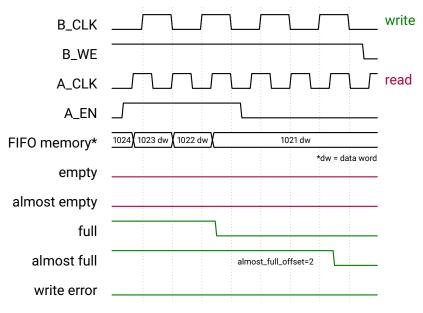

| 2.20 | Reading from a full synchronous FIFO                                                                 | 41 |

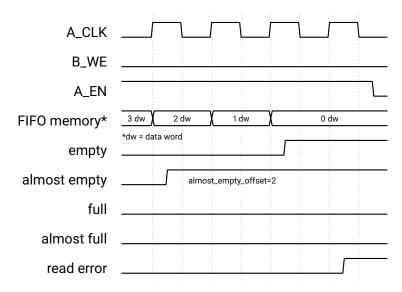

| 2.21 | Reading from an almost empty synchronous FIFO                                                              | 42 |

|------|------------------------------------------------------------------------------------------------------------|----|

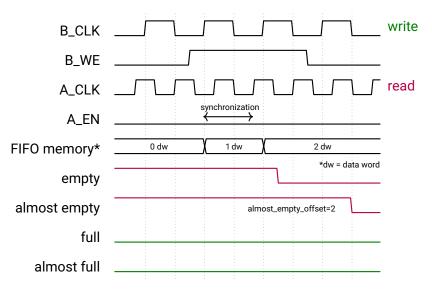

| 2.22 | Writing to an empty asynchronous FIFO                                                                      | 43 |

| 2.23 | Writing to an almost full asynchronous FIFO                                                                | 43 |

| 2.24 | Reading from a full asynchronous FIFO                                                                      | 44 |

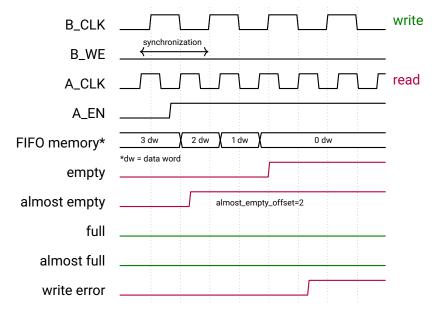

| 2.25 | Reading from an almost empty asynchronous FIFO                                                             | 44 |

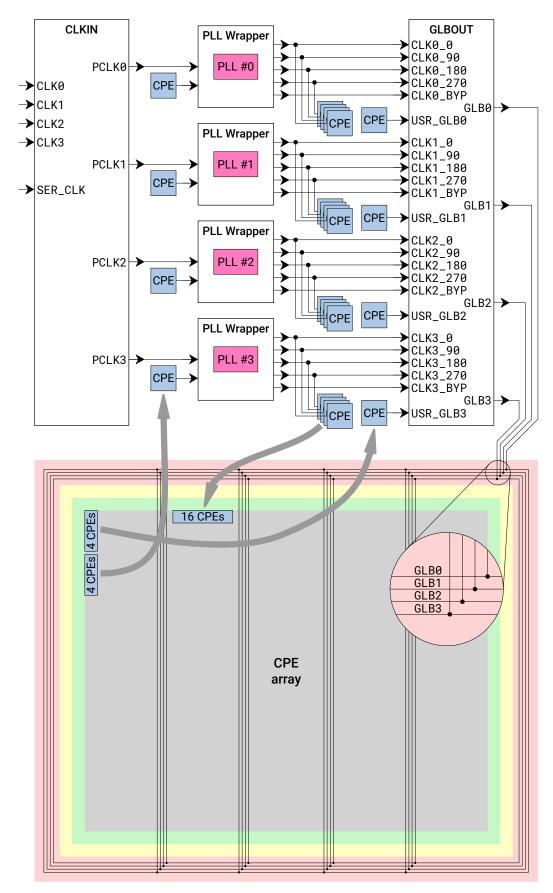

| 2.26 | Overview of the Global Mesh signal injection                                                               | 47 |

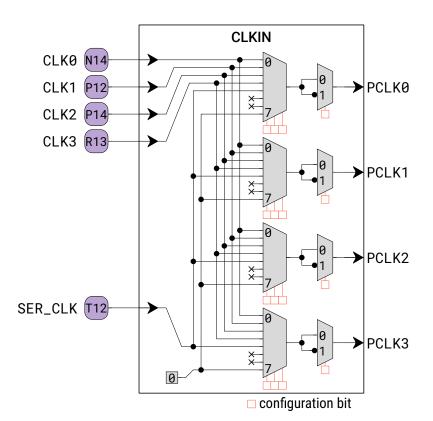

| 2.27 | Clock input multiplexers CLKIN                                                                             | 48 |

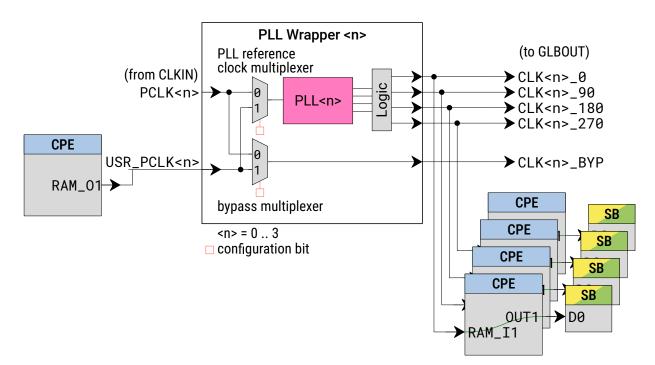

| 2.28 | phase-locked loop (PLL) wrapper with input and output clocks                                               | 48 |

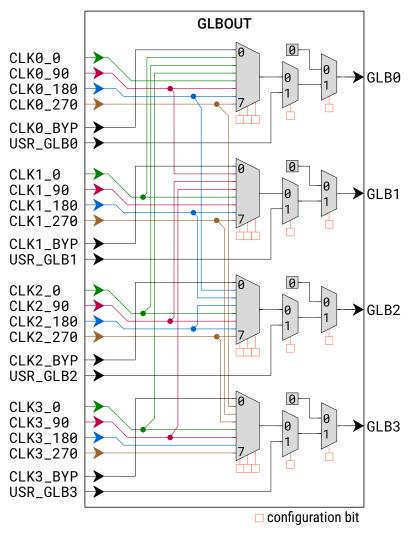

| 2.29 | GLBOUT multiplexers                                                                                        | 50 |

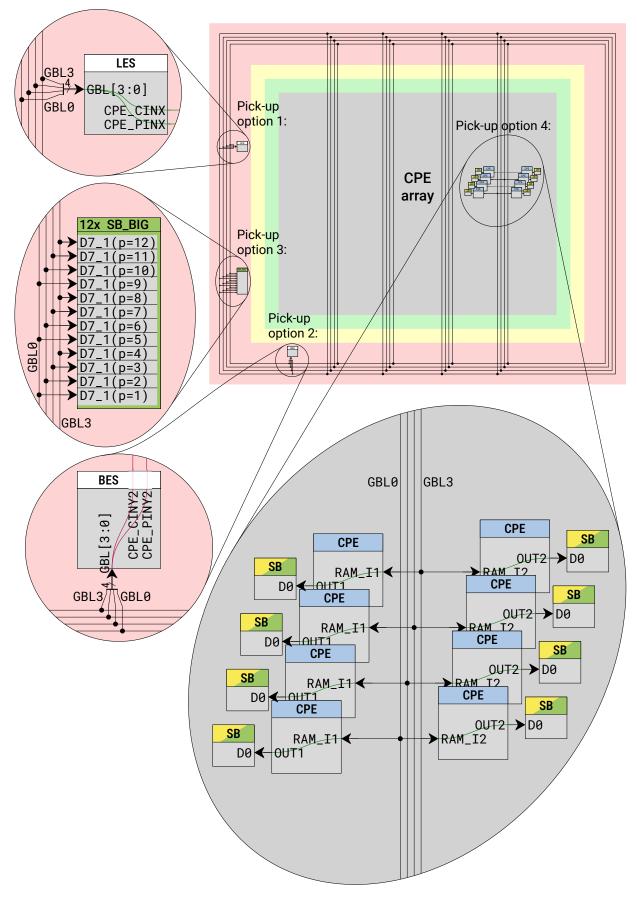

| 2.30 | Overview of signal extraction from the Global Mesh $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 53 |

| 2.31 | Intake Cologne Programmable Element (CPE) with chained CPE row $\ldots$ .                                  | 58 |

| 2.32 | Intake Bottom Edge Select (BES) with chained BES row                                                       | 59 |

| 2.33 | Unchained BES row with Global Mesh pick-up                                                                 | 60 |

| 2.34 | Intake Left Edge Select (LES) with chained CPE row                                                         | 61 |

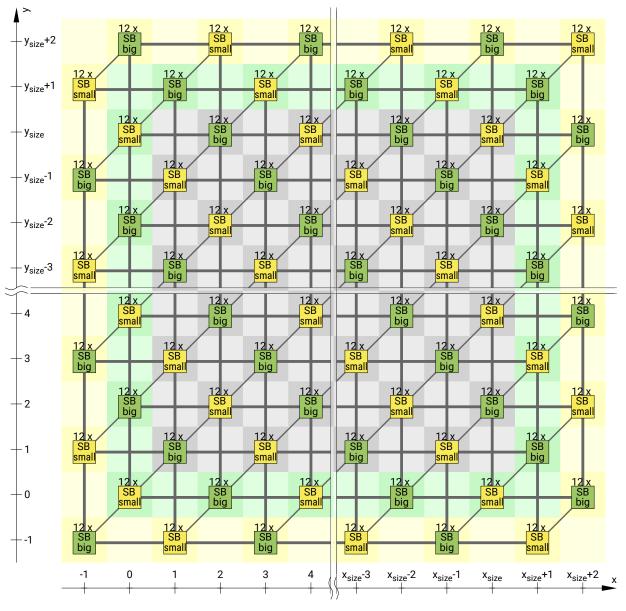

| 2.35 | Switch Box (SB) interconnection scheme                                                                     | 62 |

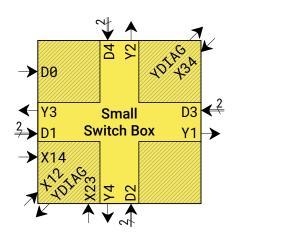

| 2.36 | Small Switch Box                                                                                           | 63 |

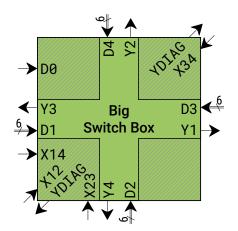

| 2.37 | Big Switch Box                                                                                             | 63 |

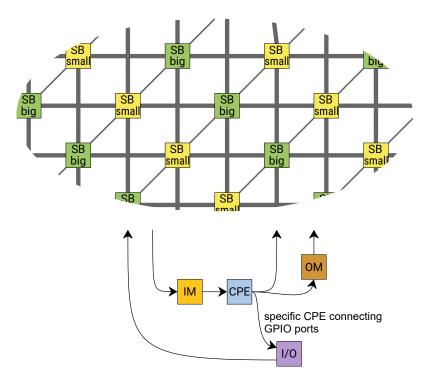

| 2.38 | CPE connections to the routing structure                                                                   | 63 |

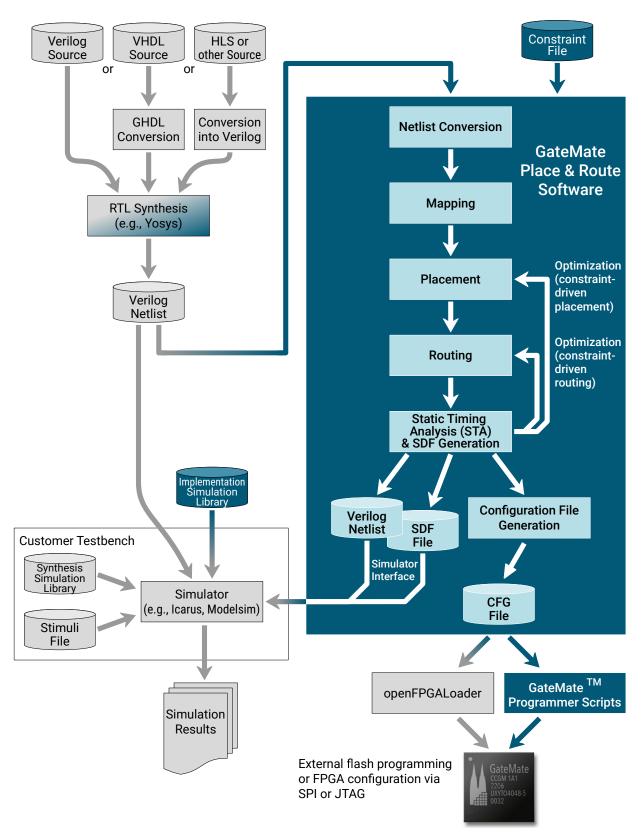

| 3.1  | GateMate <sup>TM</sup> FPGA workflow                                                                       | 66 |

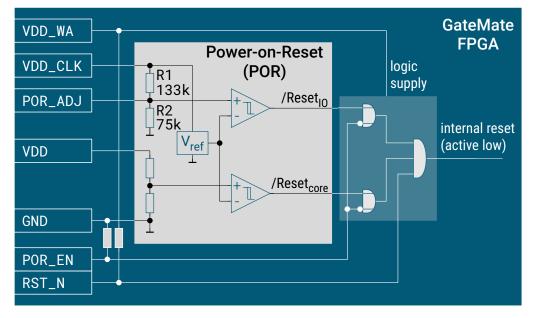

| 3.2  | Power-on reset (POR) module block diagram                                                                  | 74 |

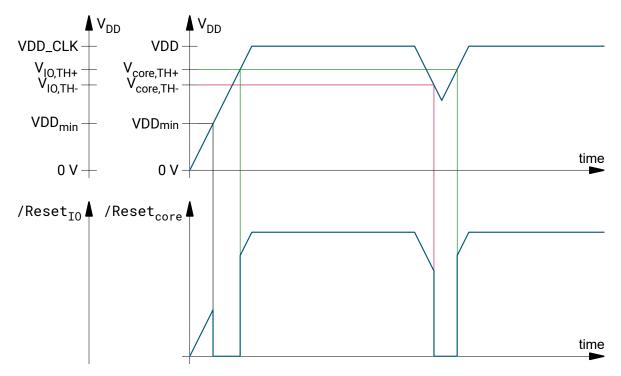

| 3.3  | Threshold principles of POR                                                                                | 75 |

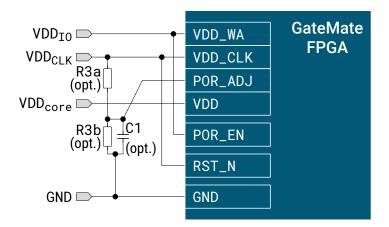

| 3.4  | FPGA reset using the POR module                                                                            | 76 |

| 3.5  | FPGA reset driven by an external logic                                                                     | 77 |

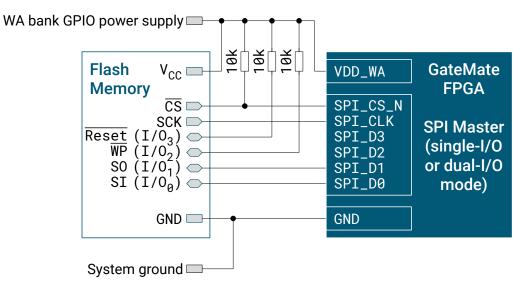

| 3.6  | Configuration data from flash memory in SPI single-I/O or dual-I/O mode $\ .\ .\ .$                        | 80 |

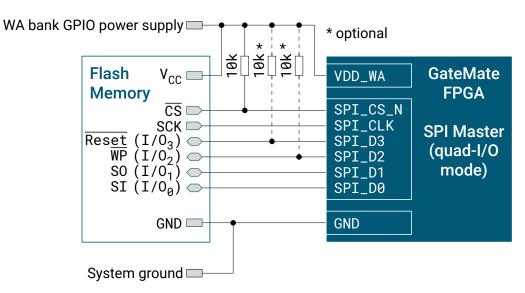

| 3.7  | Configuration data from flash memory in SPI quad-I/O mode                                                  | 80 |

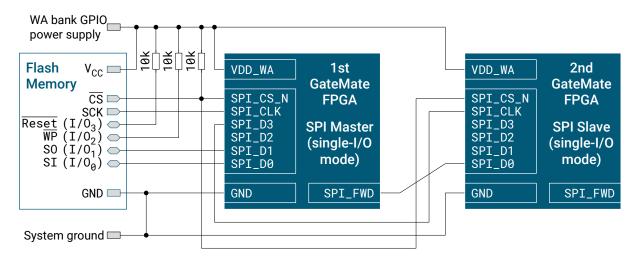

| 3.8  | Configuration data stream from a single flash memory                                                       | 81 |

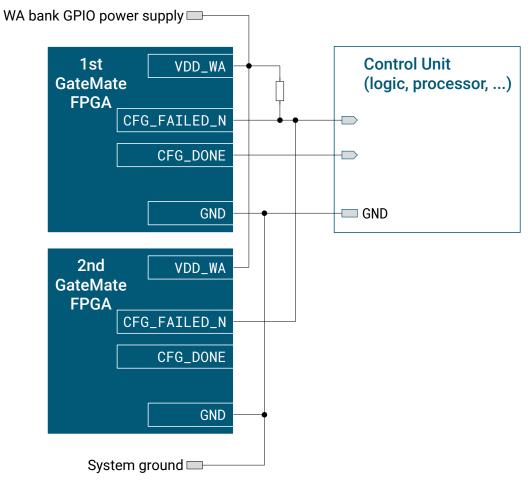

| 3.9  | Connection of CFG_DONE and CFG_FAILED_N signals in multi-FPGA applica-<br>tions with a single flash memory | 82 |

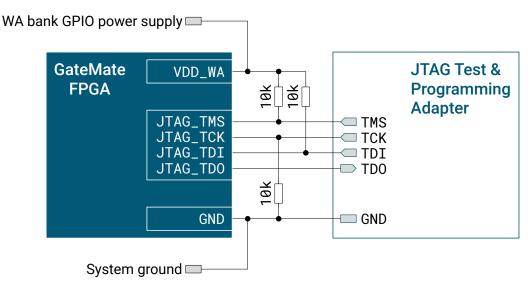

| 3.10 | JTAG connection scheme                                                                                     | 83 |

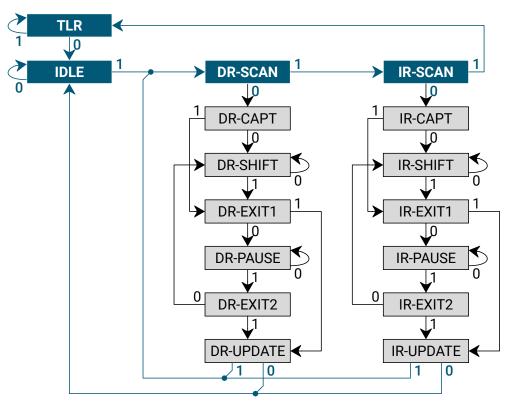

| 3.11 | Finite-state machine of the JTAG interface                                                                 | 84 |

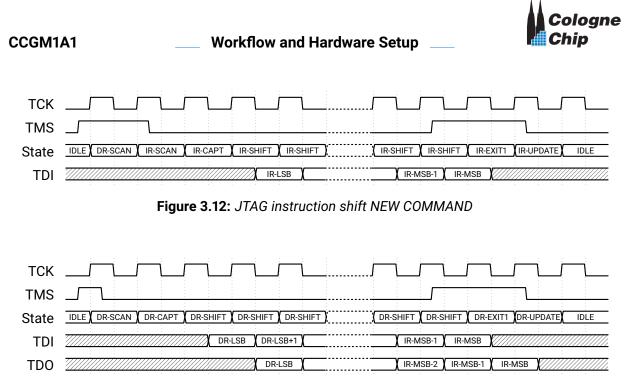

| 3.12 | JTAG instruction shift NEW COMMAND                                                                         | 85 |

| 3.13 | JTAG data shift                                                                                            | 85 |

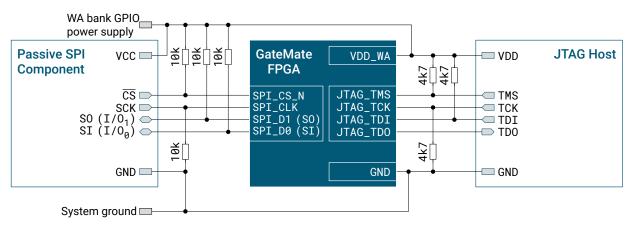

| 3.14 | JTAG-SPI bypass connection scheme                                                                          | 86 |

### List of Figures

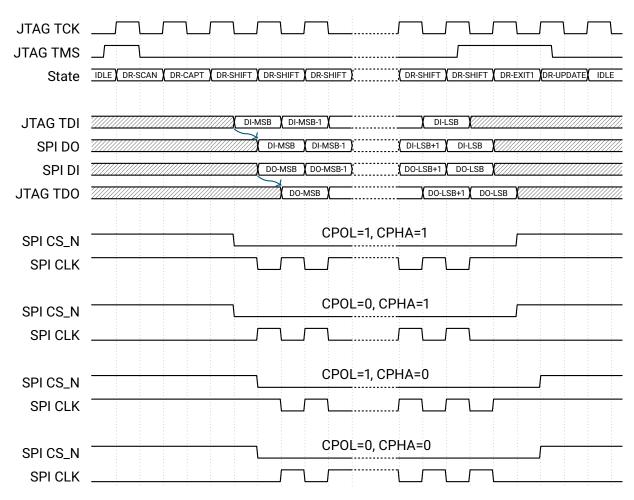

| 3.15 | Timing diagram of the JTAG-SPI bypass mode                                                    |

|------|-----------------------------------------------------------------------------------------------|

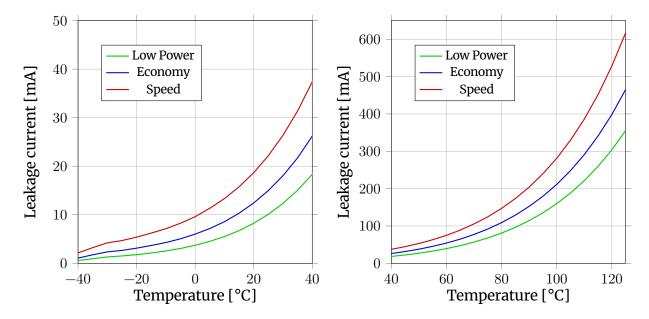

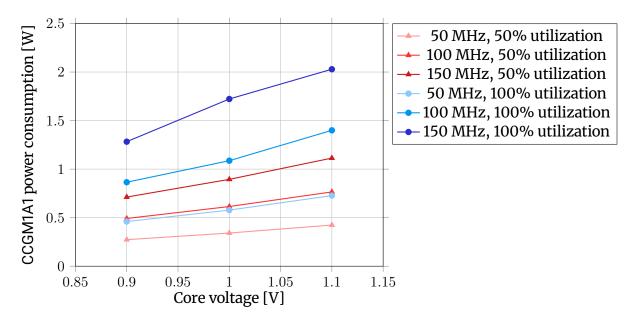

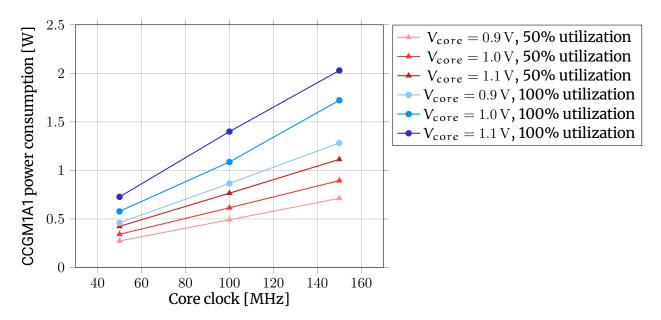

| 4.1  | CCGM1A1 leakage current                                                                       |

| 4.2  | CCGM1A1 total power consumption based on Galois-LFSR 95                                       |

| 4.3  | CCGM1A1 total power consumption based on Galois-LFSR 95                                       |

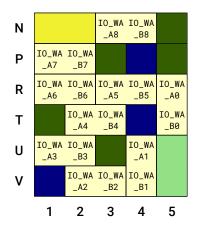

| 5.1  | CCGM1A1 FBGA pinout                                                                           |

| 5.2  | $Configuration\ pins\ of\ CCGM1A1\ FBGA\ pinout\ for\ use\ as\ GPIO\ after\ configuration100$ |

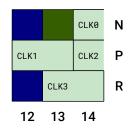

| 5.3  | Clock input pins as second function of some GPIOs                                             |

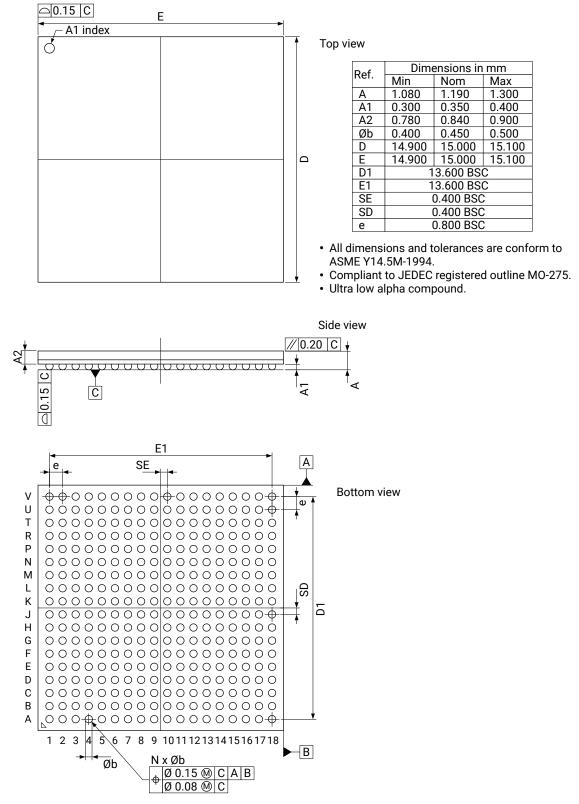

| 6.1  | FATC FBGA 324 balls package dimensions                                                        |

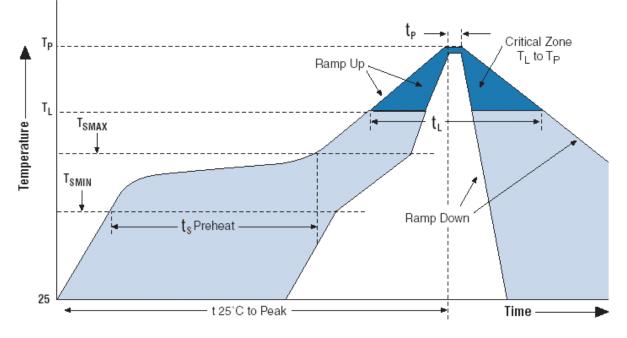

| 7.1  | Reflow soldering profile                                                                      |

# **List of Tables**

| 2.1  | 20K configurations                                                                                       | 28 |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.2  | 40K configurations                                                                                       | 28 |

| 2.3  | Input signal group                                                                                       | 29 |

| 2.4  | Pin wiring in TDP 20K mode                                                                               | 31 |

| 2.5  | Pin wiring in TDP 40K mode                                                                               | 32 |

| 2.6  | Pin wiring in SDP 20K mode                                                                               | 33 |

| 2.7  | Pin wiring in SDP 40K mode                                                                               | 33 |

| 2.8  | Access combinations in NO CHANGE mode with {A B}_EN =1 (simple dual port (SDP) and true dual port (TDP)) | 36 |

| 2.9  | Access combinations in WRITE THROUGH mode with $A B_EN = 1$ (TDP only)                                   | 36 |

| 2.10 | FIFO status flags                                                                                        | 39 |

| 2.11 | FIFO 40 bit data concatenations                                                                          | 39 |

| 2.12 | FIFO 80 bit data concatenations                                                                          | 40 |

| 2.13 | $USR\_PCLK\langle n\rangle$ sources $\ldots$                                                             | 46 |

| 2.14 | CPE destinations of PLL clock output signals                                                             | 49 |

| 2.15 | USR_GLB[3:0] sources                                                                                     | 50 |

| 2.16 | Connecting Global Mesh signals to Switch Boxes                                                           | 54 |

| 2.17 | Connecting Global Mesh signals to CPEs                                                                   | 54 |

| 2.18 | Control of the clocking scheme via CC_BUFG and carry & propagation signal lines (CP-lines)               | 55 |

| 3.1  | Configuration mode setup                                                                                 | 78 |

| 3.2 | Configuration signal bank                 | 79  |

|-----|-------------------------------------------|-----|

| 3.3 | Configuration process state               | 81  |

| 4.1 | Absolute maximum ratings                  | 93  |

| 4.2 | Operation range                           | 94  |

| 4.3 | GPIO characteristics in single-ended mode | 96  |

| 4.4 | GPIO characteristics in LVDS mode         | 96  |

| 4.5 | PLL characteristics                       | 97  |

| 4.6 | Reset characteristics                     | 98  |

| 5.1 | Pin types                                 | 101 |

| 5.2 | CCGM1A1 Pin list sorted by ball name      | 102 |

| 7.1 | Pb-free reflow soldering profile          | 116 |

## **About this Document**

This datasheet covers all features of the Cologne Chip GateMate<sup>TM</sup> FPGA Series and is part of the GateMate<sup>TM</sup> documentation collection.

For more information please refer to the following documents:

- Technology Brief of GateMate<sup>™</sup> FPGA I

- DS1002 GateMate<sup>™</sup> FPGA Programmer Board Ver. 1.3 Datasheet 🕑

- DS1003 GateMate<sup>™</sup> FPGA Evaluation Board Ver. 3.1 Datasheet Implication

- UG1001 GateMate<sup>™</sup> FPGA Primitives Library 🗹

- UG1002 GateMate<sup>™</sup> FPGA Toolchain Installation User Guide 🗹

Cologne Chip provides a comprehensive technical support. Please visit our website for more information or contact our support team.

List of Tables

### **Revision History**

This datasheet is constantly updated. The latest version of the document can be found following the link below:

DS1001 – GateMate<sup>™</sup> FPGA CCGM1A1 Datasheet ☑

| Date          | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| December 2023 | Internal pull-up/pull-down resistors of POR_EN and RST_N corrected in Figures 3.2, 3.4 and 3.5 with corresponding changes in the text of Sections 3.2.2 and 3.2.3 from page 74.                                                                                                                                                                                                                                                                          |  |  |

| November 2023 | Information added in Section 4.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| January 2023  | Minor changes in Section 3.1.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| December 2022 | <ul> <li>Section 2.6 (Global Mesh Architecture) from page 46 added.</li> <li>Section 2.7 (Clocking Schemes) from page 52 added.</li> <li>SPI_CLK (pin N4) and JTAG_TCK (pin R3) are no longer available as dedicated clock input pins.</li> <li>Chapter 7 (Soldering Guidelines) added.</li> <li>Figure 2.2 on page 22 extended by details.</li> </ul>                                                                                                   |  |  |

| May 2022      | <ul> <li>Sections 3.1.2 (Synthesis), 3.1.3 (Implementation) and 3.1.4 (Configuration) from page 67 added.</li> <li>Additional explanation to the power-on reset module: <ul> <li>Section 3.2.1 from page 74 expanded.</li> <li>Sections 3.2.2 and 3.2.2 from page 75 added.</li> <li>Reset characteristics in Table 4.6 on page 98 added.</li> </ul> </li> <li>Clock pins renamed from CLK[4:1] to CLK[3:0] (BGA pins N14, P12, P14 and R13).</li> </ul> |  |  |

| February 2022 | Updated workflow description in Section 3.1.1 from page 65 with Yosys support added.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| October 2021  | Additional explanation to Section 2.4.8 on page 36.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| July 2021     | <ul> <li>Expanded Block RAM documentation in Section 2.4 from page 27.</li> <li>Updated maximum PLL output frequencies in Section 2.5 on page 45.</li> </ul>                                                                                                                                                                                                                                                                                             |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| February 2020 | Initial pre-release.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

### **General Remarks to Notations**

- 1. The decimal point is written as a point (e.g., 1.23). Thousands separators are written with thin space.

- 2. Numerical values have different notations for various number systems; e.g., the hexadecimal value 0x C9 is 0b 1100 1001 in binary and 201 in decimal notation.

- 3. The prefix 'kilo' is written k for the meaning of 1000 and it is written K for the meaning of 1024.

- 4. Functional elements of the GateMate<sup>™</sup> FPGA have certain colors. These are:

Cologne Programmable Element (CPE)

Input Multiplexer (IM)

Output Multiplexer (OM)

Small Switch Box (SB)

Big Switch Box (SB)

General purpose input / output (GPIO)

Dual port SRAM (DPSRAM)

Phase-locked loop (PLL)

Serializer / deserializer (SerDes)

5. General purpose input / output (GPIO) banks and special pin functions of the GateMate<sup>™</sup> FPGA are grouped by certain colors. Please see Section 5.2 on page 101 for an overview.

## **Chapter 1**

## Introduction

### 1.1 Introduction

The Cologne Chip GateMate<sup>TM</sup> FPGA Series is a family of small to medium-sized FPGAs that addresses all requirements of typical applications. The programmable silicon can be used from low power to high speed applications and thus in a wide range of fields: industry, automation, communication, security, automotive, Internet of Things (IoT), artificial intelligence (AI), and lots more.

Logic capacity, power consumption, package size and printed circuit board (PCB) compatibility are optimized for a wide range of applications. As these FPGAs combine various features with lowest cost in the market, the devices are well suited from university projects to high volume applications. Because of the outstanding ratio of circuit size to cost, even price sensitive applications can also now take advantage of FPGAs. The devices are manufactured using Globalfoundries<sup>TM</sup> 28 nm Super Low Power (SLP) process in Dresden, Germany. The GateMate<sup>TM</sup> FPGA program is supported by the German Federal Ministry for Economic Affairs and Energy as part of the Important Project of Common Eu-

Supported by:

on the basis of a decision by the German Bundestag

ropean Interest (IPCEI) on Microelectronics project, which is also supported by the European Commission.

Cologne Chip is a semiconductor company based in Cologne, Germany. The company, which celebrates its 25th anniversary in 2020, has excellent industry knowledge and an experienced team of developers. The design and manufacturing location *Made in Germany* represents a unique selling proposition of globally competitive FPGAs in the market.

Cologne Chip offers and supports a variety of development tools:

- The GateMate<sup>™</sup> FPGA Evaluation Board is a feature-rich, ready-to-use development platform that serves as a reference design and for a direct entry into application development.

- With the help of the GateMate<sup>™</sup> FPGA Programmer, the FPGA can be configured in various ways.

Cologne Chip provides a comprehensive technical support. Please visit our website for more information or contact our support and sales teams.

### 1.2 Features

- Novel programmable element architecture

- 20,480 programmable elements for combinatorial and sequential logic

- · 20,480 8-input LUT-trees / 40,960 4-input LUT-trees

- 40,960 Latches / Flip-flops within programmable elements

- Each programmable element configurable as:

- 1-bit full adder

- 2-bit full adder or

- 2×2-bit multiplier

- Dedicated logic and routing for fast arithmetic and arbitrary-sized multipliers

- 9 general purpose input / output (GPIO) banks

- 162 user-configurable GPIOs

- All GPIOs configurable as single-ended or LVDS differential pairs

- Double data rate (DDR) registers in I/O cells

- I/O voltage range from 1.2 to 2.5 V

- 4 clock generators (PLL)

- Maximum PLL output frequency from 250 MHz to 416.75 MHz

- 2.5 Gb/s serializer / deserializer (SerDes) controller

- Flexible memory resources

- 1,310,720 total RAM bits distributed over 32 SRAM blocks

- Each RAM block configurable as two independent 20 Kbit blocks or single 40 Kbit block

- Simple or True Dual Port (SDP / TDP) or FIFO mode

- Data width from 1 bit up to 40 bits (TDP) or 80 bits (SDP)

- Bit-wide write enable

- Error checking and correcting (ECC) for certain bit widths

- Flexible device configuration

- Configuration bank switchable to user I/O

- JTAG interface with bypass to SPI interface

- Active / passive SPI interface for singe-, dual- and quad-mode operation

- SPI flash interface in active mode

- Multi-chip configuration from single source

- Application modes: low power, economy, speed

- Mode adjustable on each chip via core voltage

- Core voltage range from 0.9 to 1.1 V

- Package

- 15×15 mm 324 balls 0.8 mm fine pitch Ball Grid Array (FBGA) package

- Only 2 signal layers required on PCB

# **Chapter 2**

## Architecture

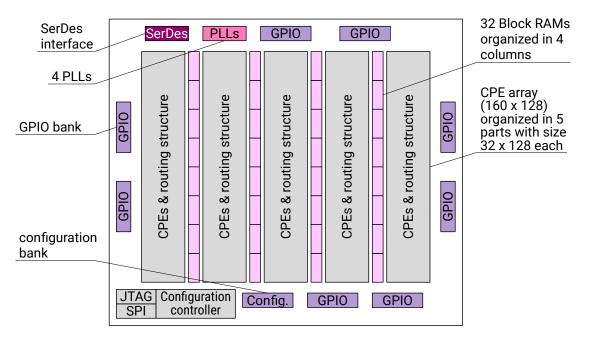

### 2.1 GateMate<sup>™</sup> FPGA Overview

The basic functional elements of GateMate<sup>TM</sup> FPGA are set up in an array structure of  $160 \times 128$  elements called Cologne Programmable Element (CPE) as described in Section 2.2.

All CPEs are interconnected by a routing structure of  $132 \times 164$  so-called Switch Boxes (SBs) as described in Section 2.8.

Additional functional blocks are dual port SRAMs (DPSRAMs), phase-locked loops (PLLs), general purpose input / output (GPIO) cells, SPI configuration and data flash interface, JTAG interface and serializer / deserializer (SerDes) interface.

Figure 2.1: Simplified architecture overview

### 2.2 Cologne Programmable Element (CPE)

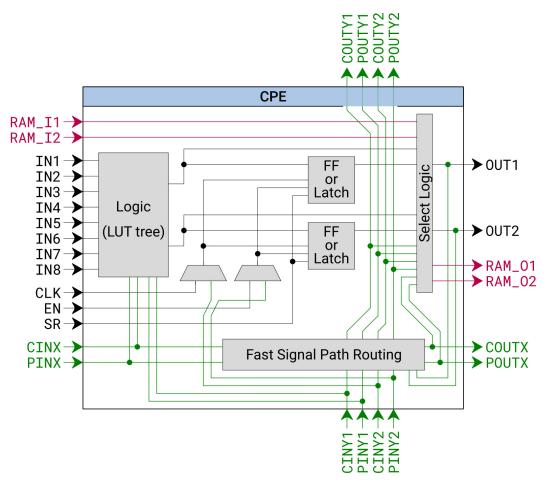

General purpose combinatorial and sequential circuits are implemented using CPEs. The CCGM1A1 has 20,480 CPEs arranged in a  $160 \times 128$  matrix. Each CPE can be set up to the following combinatorial functions:

- Dual 4 inputs with 2-input lookup table (LUT-2) tree each

- 8 inputs with LUT-2 tree

- 6 inputs with 4-input multiplexer (MUX-4) function

- 1-bit or 2-bit full adder, expandable to any length in horizontal or vertical arrangement

- +  $2 \times 2$ -bit multiplier, expandable to any multiplier size

Figure 2.2 illustrates the general structure of a CPE. General combinatorial and sequential functions are supported from fast signal path routing. In addition, the DPSRAM blocks of GateMate<sup>™</sup> FPGA, as described in Chapter 2.4, require some CPE ports RAM\_I[2:1] and RAM\_0[2:1] for CPE-to-SRAM connection.

Figure 2.2: Cologne Programmable Element (CPE)

Two CPE outputs 0UT1 and 0UT2 are available and each can use a Flip-Flop or Latch function.

Furthermore, the CPEs include fast signal routing paths, so-called carry & propagation signal lines (CP-lines). Typically, they are used for fast clock and carry propagation in adder and multiplier functions, e.g., fast CPE to adjacent CPE connections, or even fast signal propagation over any span of CPEs.

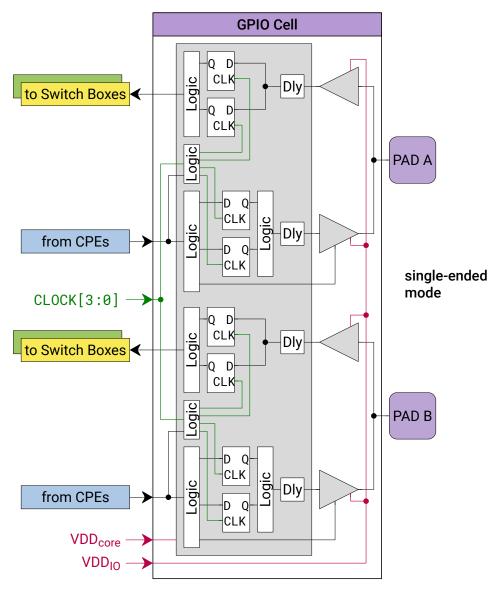

### 2.3 General purpose input / output (GPIO)

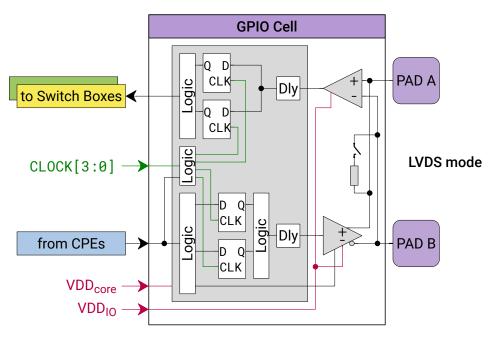

The GateMate<sup>™</sup> FPGA offers up to 162 general purpose input / output pins (GPIOs). These are organized in signal pairs, so-called *pad cells*, which can either operate as two independent, bidirectional single-ended signals or they can be set up as bidirectional low-voltage differential signaling (LVDS). Figures 2.3 and 2.4 show the structure of the pad cells and their interconnection to the FPGA elements.

Figure 2.3: GPIO cell in single-ended mode

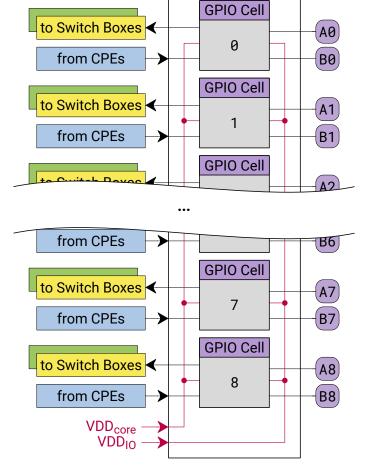

Nine pad cells build up a GPIO bank as shown in Figure 2.5 on page 26. Eight banks and another optional bank<sup>1</sup> are available.

<sup>&</sup>lt;sup>1</sup> The FPGA configuration pins are arranged within the ninth GPIO bank. These pins can be used as normal GPIO bank after configuration process.

The single-ended GPIO support the low voltage CMOS (LVCMOS) standard up to 2.5 V nominal supply voltage, compliant to the standards JESD8-5 (2.5 V) and JESD8-7 (1.8 V and 1.2 V).

Figure 2.4: GPIO cell in LVDS mode

The single-ended GPIO pins have the following output features:

- 0/1/high-Z

- Slew-rate control

- + Driver strength 3 mA, 6 mA, 9 mA and 12 mA

- 2 Flip-Flops

- Programmable delay line

The single-ended GPIO pins have the following input features:

- Schmitt-trigger input

- Pull-up/pull-down resistors or keeper functionality

- Input receiver disable for power reduction

- 2 Flip-Flops

- Programmable delay line

If a pad cell is used in its LVDS mode, both pads can be used together only. The LVDS pad is compliant to the LVDS 2.5 V standard. It further can operate down to 1.8 V nominal supply voltage, with common mode voltage  $V_{DD}/2$ . The LVDS input receiver can be used as voltage comparator.

**GPIO Bank**

Figure 2.5: GPIO bank

### 2.4 Embedded Block RAM

#### 2.4.1 Block RAM Overview

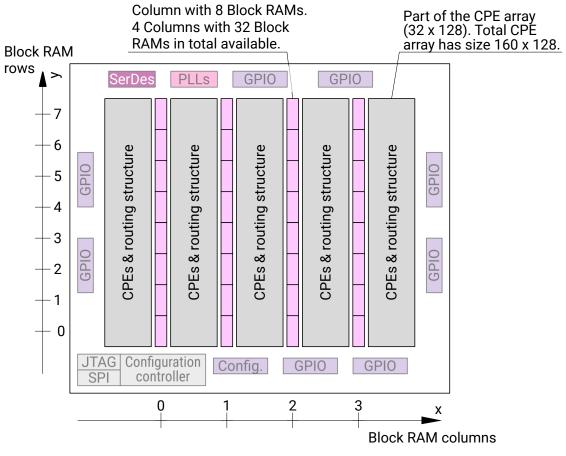

The GateMate<sup>TM</sup> FPGA contains a number of embedded volatile memory cells which are organized as configurable 40 kbit dual port SRAM (DPSRAM) cells. These random-access memory (RAM) cells are arranged in columns between the CPE array and routing structure as illustrated in Figure 2.6. Block RAMs have an address (x, y) with x = 0...3 and y = 0...7.

Figure 2.6: Block RAM arrangement

Each Block RAM cell can be configured as a single 40K or two independent 20K DPSRAM cells. Both allow usage of the memory in true dual port (TDP) or simple dual port (SDP) mode.

The GateMate<sup>™</sup> Block RAM features include:

- Data widths from 1 bit up to 40 bits in TDP mode or 80 bits in SDP mode.

- Bit-wide write enable allows a bit-wise writing of incoming data and can be used when for example interfacing with a microprocessor.

- Each port has optional output registers. When enabled, validity of the output data gets delayed by one clock cycle. This feature is particularly helpful when dealing with critical paths.

- Each port provides an error checking and correcting (ECC) module for data protection against unintended changes. Error correction is able to correct one bit errors and detect two bit errors.

- A memory cascading feature connects adjacent RAM cells to form a larger array. This feature enables the instantiation of deeper or wider memories and a flexible forwarding of clocks, address and control signals.

- Two adjacent Block RAMs can be combined to one deeper  $64K \times 1$  memory by extending the cascade feature to forward data and bitmask signals as well.

- Contents of the Block RAM cells can be initialized during configuration, e.g., to build read-only memory (ROM).

- All clock, enable and write enable signals can be inverted individually.

- Each Block RAM can be used as a first-in, first-out memory (FIFO) in asynchronous or synchronous mode with dedicated status signals for FIFO monitoring and reset.

Tables 2.1 and 2.2 show the available address and data bus width configurations as well as the ECC availability for both 20K and 40K configurations in SDP and TDP modes.

| Configuration              | TDP          | SDP | ECC |  |  |

|----------------------------|--------------|-----|-----|--|--|

| (RAM size per 20K block)   |              |     |     |  |  |

| $16K \times 1 \text{ bit}$ | $\checkmark$ | 1   | ×   |  |  |

| $8K \times 2$ bit          | $\checkmark$ | 1   | ×   |  |  |

| $4K \times 5$ bit          | $\checkmark$ | 1   | ×   |  |  |

| $2K \times \ 10 \ bit$     | $\checkmark$ | 1   | ×   |  |  |

| $1K\times 20bit$           | $\checkmark$ | 1   | ×   |  |  |

| $512\times40bit$           | ×            | 1   | 1   |  |  |

| Table 2.1: 20K | configurations |

|----------------|----------------|

|----------------|----------------|

| Configuration              | TDP | SDP | ECC |

|----------------------------|-----|-----|-----|

| $32K \times 1$ bit         | 1   | 1   | X   |

| $16K \times 2$ bit         | 1   | 1   | ×   |

| $8K \times 5$ bit          | 1   | 1   | X   |

| $4K \times 10$ bit         | 1   | 1   | X   |

| $2K\times 20bit$           | 1   | 1   | X   |

| $1K \times 40 \text{ bit}$ | 1   | 1   | 1   |

| $512\times80$ bit          | X   | 1   | 1   |

Table 2.2: 40K configurations

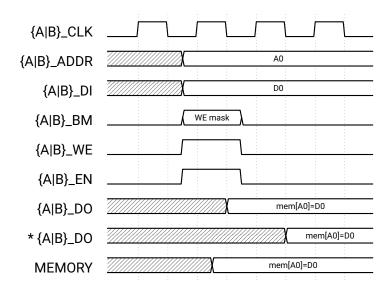

### 2.4.2 Block RAM Architecture

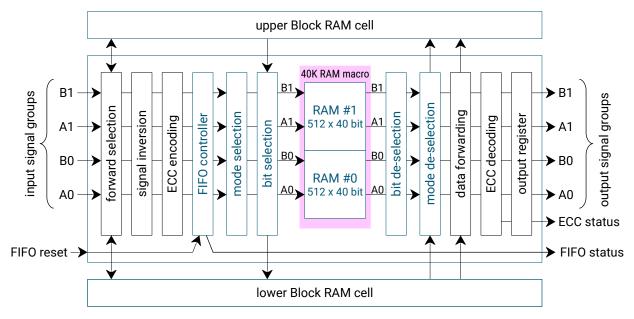

A Block RAM cell has a maximum storage capacity of 40 Kbits and can be configured as a single 40K cell or two independent 20K cells. It contains two independent ports A and B that are implemented in the form of the four input signal groups A0, B0, A1 and B1. Configured as two independent 20K cells, A0, B0, A1 and B1 represent ports A and B for the two cells. In the 40K configuration, A0+A1 and B0+B1 are combined to represent both ports A and B. Figure 2.7 shows the basic structure of a single Block RAM cell with its horizontal input and output connections from the CPE array and to the routing structure as well as the vertical interconnection to adjacent Block RAM cells.

Figure 2.7: High level block diagram of a block RAM cell

The memory inputs can each be fed in from the CPE outputs RAM\_01 or RAM\_02. Each of the control and address signals CLK, EN, WE and ADDR can be selected from two input connections.

| Signals                 | Width | Description                    |

|-------------------------|-------|--------------------------------|

| {a0,a1,b0,b1}_clk{1,2}  | 1     | Clock signal                   |

| {a0,a1,b0,b1}_en{1,2}   | 1     | Enable signal                  |

| {a0,a1,b0,b1}_we{1,2}   | 1     | Write enable signal            |

| {a0,a1,b0,b1}_addr{1,2} | 16    | Address bus                    |

| {a0,a1,b0,b1}_di        | 20    | Data bus                       |

| {a0,a1,b0,b1}_bm        | 20    | Mask for bit-wise write enable |

|                         |       |                                |

| Table 2.3: Inpu | ıt signal group |

|-----------------|-----------------|

|-----------------|-----------------|

Data output signals and status output signals such as ECC and FIFO flags are connected via the CPE inputs RAM\_I1 and RAM\_I2 to the Switch Boxes (SBs) of the routing structure.

The entire functionality of the Block RAM is implemented over several layers around the RAM cores. The forward selection part allows a flexible switching between several incoming signals of which one can be selected and forwarded to the next layers. This corresponds to the clock, enable, write enable, address, data and bitmask signals. The forward selection determines whether signals (a) from an adjacent RAM cell, e.g., to allow the building of wider or deeper memories, or (b) from the CPE array via the input signal groups A0, A1, B0 and B1 are routed to the next layers.

In the signal inversion block the clock, enable and write enable signals are individually

inverted depending on the configuration.

The Block RAM provides an internal ECC encoding and decoding layer to protect data against corruption. Depending on the configuration, 8 or 16 bits are required for storage of the parity bits. This feature is therefore only available for data widths of 40 or 80 bits as shown in Tables 2.1 and 2.2. Due to the storage of the parity bits, the actual net data width is 32 or 64 bits. Error correction is implemented using Hamming-code (39,32) with 7 parity bits. It can correct one bit error and detect two bit errors. The error status can be queried via the corresponding output signals. Section 2.4.7 describes the ECC features in more detail.

With the FIFO feature enabled, the internal write and read pointers will be forwarded to the memory macros. The address signals are therefore ignored. Port B is the push while port A is the pop side. The FIFO is configurable to be synchronous or asynchronous. Additional flags indicate the current status, such as empty, full, almost empty, almost full, read error, write error as well as the current FIFO read and write pointers. Moreover, the FIFO controller has a dedicated active low reset signal FIFO\_RST\_N. Section 2.4.9 describes the FIFO features in more detail.

The mode selection part forwards the incoming signals of ports A0, A1, B0 and B1 to the 8 ports of the memory hard macros according to the selected mode. Sections 2.4.3 and 2.4.4 describe the TDP and SDP modes in more detail.

Each port has an optional output register to improve design performance. If enabled, validity of the output data and ECC status flags get registered and thus delayed by one clock cycle.

### 2.4.3 TDP Mode

Block RAM in true dual port (TDP) mode supports simultaneous read and write operations and has two independent access ports. Figures 2.8 and 2.9 illustrate the TDP data flow in both 20K and 40K configurations.

Data can be read to or written from both ports at the same time. Read access to one port while writing to the other is also possible. Both ports can have separate clocks and input and output data widths may be different. Thus, the clocks can be synchronous or asynchronous. Both ports have access to the entire memory at any time.

There is no internal conflict handling when accessing the same address at the same time. Such simultaneous accesses can result in data uncertainty and should be avoided.

If split into two independent 20K cells, the maximum data width per port is 20 bits. In the 40K configuration, the maximum data width per port is 40 bits.

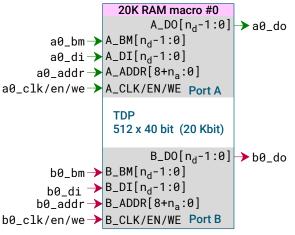

Table 2.4 shows the data and address bus wiring in TDP 20K mode when using half Block RAM #0. Control signals are a0\_clk, a0\_en and a0\_we. The wiring of a0\_di also applies to the a0\_bm signals. The wiring for the other half Block RAM #1 ports A1 and B1 is equivalent.

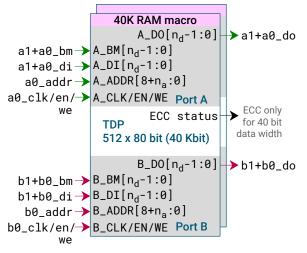

Table 2.5 shows the data and address bus wiring in TDP 40K mode when using ports A0 and A1 to form port A. Control signals are a0\_clk, a0\_en and a0\_we. Note that due to

Data width:  $n_d = 1 ... 20$ Address width:  $n_a = 0 ... 5$ Separate values  $n_d$  and  $n_a$  for ports A and B as well as for data read and write accesses.

Same for RAM #1, where all signals a0\_\* and b0\_\* are a1\_\* and b1\_\* .

**Figure 2.8:** Internal data flow of DPSRAM in TDP 20K mode

Data width:  $n_d = 1 ... 40$ Address width:  $n_a = 0 ... 6$ Separate values  $n_d$  and  $n_a$  for ports A and B as well as for data read and write accesses.

**Figure 2.9:** Internal data flow of DPSRAM in TDP 40K mode

the port combining, the maximum data width per port is 40 bits. The wiring of a0\_di also applies to the a0\_bm signals. The wiring for port B, which is formed by B0 and B1, is equivalent.

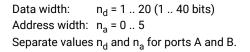

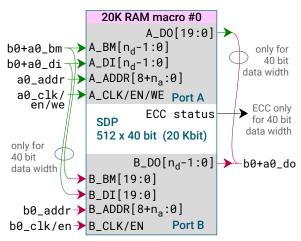

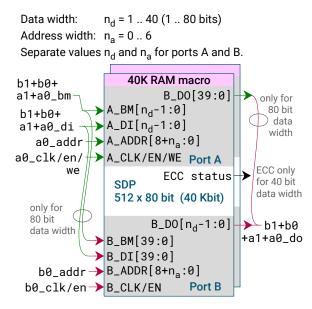

#### 2.4.4 SDP Mode

Block RAM in simple dual port (SDP) mode supports simultaneous read and write operations, but has a single output port for read data. By that, data widths can be doubled compared to the TDP mode.

| Width | Depth    | Address-in bus <sup>1</sup>  | Data-in bus <sup>1</sup> | Data-out bus <sup>1</sup> |

|-------|----------|------------------------------|--------------------------|---------------------------|

| 1     | - 16,384 | a0_addr[15:7]∘a0_addr[5:1]   | a0_di[0]                 | a0_do[0]                  |

| 2     | •        | a0_addr[15:7] o a0_addr[5:2] |                          | a0_do[1:0]                |

| 5     | 4,096    | a0_addr[15:7]oa0_addr[5:3]   | a0_di[4:0]               | a0_do[4:0]                |

| 10    | 2,048    | a0_addr[15:7]∘a0_addr[5:4]   | a0_di[9:0]               | a0_do[9:0]                |

| 20    | 1,024    | a0_addr[15:7]∘a0_addr[5]     | a0_di[19:0]              | a0_do[19:0]               |

Table 2.4: Pin wiring in TDP 20K mode

<sup>1</sup> Symbol  $\circ$  is concatenation.

Same for RAM #1, where all signals a0\_\* and b0\_\* are a1\_\* and b1\_\* .

**Figure 2.10:** Internal data flow of DPSRAM in SDP 20K mode

**Figure 2.11:** Internal data flow of DPSRAM in SDP 40K mode

Port A is always the write port, while port B is always the read port. Both write and read ports can have separate clocks. The write port A uses the enable signal  $\{a0, a1\}$ \_en and write enable signal  $\{a0, a1\}$ \_we for write access and the read port B uses only the enable signal  $\{b0, b1\}$ \_en for read access.

Table 2.6 shows the data and address bus wiring in SDP 20K mode. By combining the data buses on ports A0 and B0, the maximum bus width can be doubled compared to the TDP mode. Control signals for the write port A are a0\_clk, a0\_en and a0\_we. Control signals for the read port B are b0\_clk and b0\_en. The wiring of {a0, b0}\_di also applies to the {a0, b0}\_bm signals. The wiring for ports A1 and B1 is equivalent.

| Width | Depth  | Address-in bus | Data-in bus <sup>1</sup> | Data-out bus <sup>1</sup> |

|-------|--------|----------------|--------------------------|---------------------------|

| 1     | 32,768 | a0_addr[15:1]  | a0_di[0]                 | a0_do[0]                  |

| 2     | 16,384 | a0_addr[15:2]  | a0_di[1:0]               | a0_do[1:0]                |

| 5     | 8,192  | a0_addr[15:3]  | a0_di[4:0]               | a0_do[4:0]                |

| 10    | 4,096  | a0_addr[15:4]  | a0_di[9:0]               | a0_do[9:0]                |

| 20    | 2,048  | a0_addr[15:5]  | a0_di[19:0]              | a0_do[19:0]               |

| 40    | 1,024  | a0_addr[15:6]  | a1_di[19:0]              | a1_do[39:0]               |

|       |        |                | ∘a0_di[19:0]             | ∘a0_do[39:0]              |

<sup>1</sup> Symbol  $\circ$  is concatenation.

Table 2.7 shows the data and address bus wiring in SDP 40K mode. By combining the data buses on all ports A0, B0, A1 and B1, the maximum bus width can be doubled compared to the TDP mode. Control signals for the write port A are A0\_CLK, A0\_EN and A0\_WE. Control signals for the read port B are b0\_clk and b0\_en. The wiring of {a0, a1, b0, b1}\_di also applies to the {a0, a1, b0, b1}\_bm signals.

#### 2.4.5 Expanding Data Widths and Cascade Mode

The Block RAM allows the coupling of adjacent Block RAMs to build larger or deeper memories by forwarding clock, enable, write enable and address signals. This feature facilitates the routing in the CPE array and the routing structure for the signals mentioned.

The cascade mode extends this feature by forwarding data and bitmask as well. It only allows a data width of 1 bit. Cascading is only possible in the lower direction, as shown in Figure 2.12 on page 34. By that, two adjacent  $32K \times 1$  bit Block RAM cells can be combined to form a  $64K \times 1$  bit memory. The actual data and bitmask inputs and outputs of the cascade are the data and bitmask inputs and outputs of the upper RAM cell. Prerequisite is that both RAM cells involved are configured in  $32K \times 1$  bit TDP mode. Bit 0 of the address bus selects the upper or lower Block RAM cell for the write or read operation.

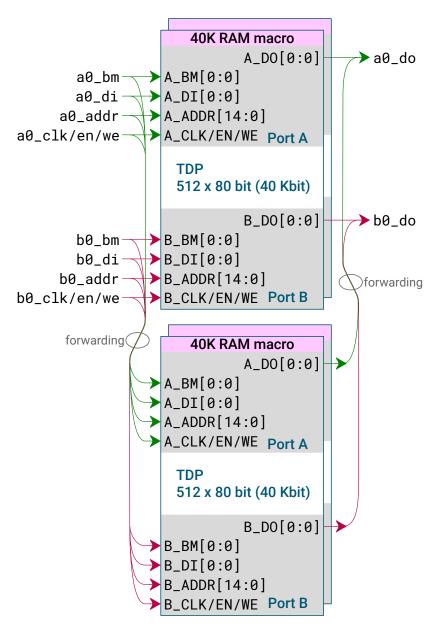

#### 2.4.6 Memory Mapping and Content Initialization

Each port can access a certain memory area depending on its configuration. The addressing scheme depends on the configuration mode. Words of 5, 10, 20, 40 and 80<sup>2</sup> bits are

| Width | Depth | Address-in bus     | Data-in bus <sup>1</sup> | Data-out bus <sup>1</sup> |

|-------|-------|--------------------|--------------------------|---------------------------|

| 40    | 512   | {b0,b0}_addr[15:7] | b0_di[19:0]              | b0_do[19:0]               |

|       |       |                    | ∘a0_di[19:0]             | ∘a0_do[19:0]              |

| Table 2.6: | Pin | wiring | in | SDP | 20K | mode |

|------------|-----|--------|----|-----|-----|------|

|------------|-----|--------|----|-----|-----|------|

<sup>1</sup> Symbol  $\circ$  is concatenation.

| Table 2.7: Pir | n wiring in | SDP 40K | mode |

|----------------|-------------|---------|------|

|----------------|-------------|---------|------|

| Width | Depth | Address-in bus     | Data-in bus <sup>1</sup> | Data-out bus <sup>1</sup> |

|-------|-------|--------------------|--------------------------|---------------------------|

| 80    | 512   | {b0,a0}_addr[15:7] | b1_di[19:0]              | b1_do[19:0]               |

|       |       |                    | ∘b0_di[19:0]             | ∘b0_do[19:0]              |

|       |       |                    | ∘a1_di[19:0]             | ∘a1_do[19:0]              |

|       |       |                    | ∘a0_di[19:0]             | ∘a0_do[19:0]              |

<sup>1</sup> Symbol  $\circ$  is concatenation.

<sup>&</sup>lt;sup>2</sup> Data width of 80 bits only supported in 40K SDP mode (see Tables 2.1 and 2.2).

Figure 2.12: Structure of two adjacent DPSRAMs forming one  $64K \times 1$  bit memory via cascade feature

distributed equally over all four static random-access memory (SRAM) blocks whereas 1 and 2 bit wide words are arranged so that every 5th bit is not accessible. This leads to a logical mapping of the memory bits as shown in Figure 2.13 on page 35. The scheme shown here can be applied to both SDP and TDP modes in 20K as well as in 40K configurations.

### 2.4.7 ECC Encoding / Decoding

The Block RAM cell provides an internal ECC encoding and decoding layer to protect data against corruption. If configured, parity bits are generated and checked automatically. Using this feature, the user cannot utilize the all 40 or 80 data bits but must restrict to

Architecture

| Port<br>Width   | Logical Mapping                                                                                                                                                                    |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 Bit<br>2 Bits | x 63 62 61 60 x 59 58 57 56 x 55 54 53 52 x 51 50 49 48 x 47 46 45 44 x 43 42 41 40 x 39 38 37 36 x 35 34 33 32<br>x 31 30 x 29 28 x 27 26 x 25 24 x 23 22 x 21 20 x 19 18 x 17 16 |  |  |

| 5 Bits          | 15 14 13 12 11 10 9 8                                                                                                                                                              |  |  |

| 10 Bits         | 7 6 5 4                                                                                                                                                                            |  |  |

| 20 Bits         | 3 2                                                                                                                                                                                |  |  |

| 40 Bits         | 1                                                                                                                                                                                  |  |  |

| 80 Bits         | 0                                                                                                                                                                                  |  |  |

| Bit<br>Location | 191817161514131211109876543210<br>Dual Port SRAM #1 - 512 x 40 bit                                                                                                                 |  |  |

|                 |                                                                                                                                                                                    |  |  |

| 1 Bit           | x 31302928 x 27262524 x 23222120 x 19181716 x 15141312 x 1110 9 8 x 7 6 5 4 x 3 2 1 0                                                                                              |  |  |

| 2 Bits          | x 15 14 x 13 12 x 11 10 x 9 8 x 7 6 x 5 4 x 3 2 x 1 0                                                                                                                              |  |  |

| 5 Bits          | 7 6 5 4 3 2 1 0                                                                                                                                                                    |  |  |

| 10 Bits         | 3 2 1 0                                                                                                                                                                            |  |  |

| 20 Bits         | 1 0                                                                                                                                                                                |  |  |

| 40 Bits         | 0                                                                                                                                                                                  |  |  |

| 80 Bits         | 0                                                                                                                                                                                  |  |  |

| Bit<br>Location | 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br>Dual Port SRAM #0 - 512 x 40 bit                                            |  |  |

|                 | Pia anterio il la                                                                                                                                                                  |  |  |

X Bit not accessible

32 or 64 bits since the remaining 8 or 16 bits are required for storage of parity bits. This feature is only available for the following configurations:

- TDP 40K, configured to 40 bits of which user can only use 32 bits

- SDP 40K, configured to 80 bits of which user can only use 64 bits

- SDP 20K, configured to 40 bits of which user can only use 32 bits

In any case the bitmask is ignored, all 32 or 64 bits plus parity are written to memory. For error correction the Hamming-code (39,32) with 7 parity bits is used. It can correct one bit error and detect two bit errors. If one error was detected the ECC single error flag signal will be logic true. If two errors were detected the ECC double error flag will be logic true. There are two dedicated status signals {A,B}\_ECC\_{1B,2B}\_ERR for single and double error flags each, which are utilized in the following way:

- TDP 40K, data width 40 bits: status signal A\_ECC\_{1B, 2B}\_ERR indicate errors at port A while B\_ECC\_{1B, 2B}\_ERR indicate errors at port B

- SDP 40K, data width 80 bits: status signal A\_ECC\_{1B,2B}\_ERR indicate errors while B\_ECC\_{1B,2B}\_ERR are don't care

- SDP 20K, data width 40 bits: status signal A\_ECC\_{1B, 2B}\_ERR indicate errors at half Block RAM #0 while B\_ECC\_{1B, 2B}\_ERR indicate errors at half Block RAM #1

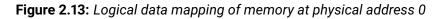

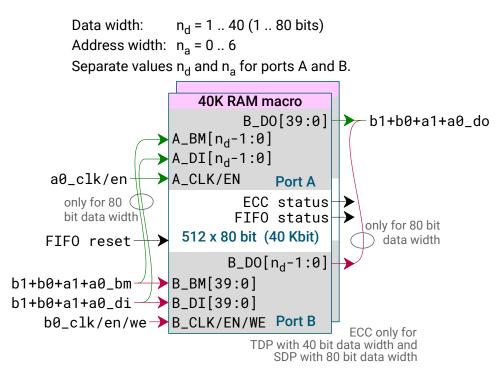

### 2.4.8 RAM Access Modes and Enable

A block RAM cell has three signals to control read and write access.  $\{A | B\}_EN$  is a global enable signal. It is required to be active during any read or write access.  $\{A | B\}_WE$  is a global write enable signal that operates in association with the bit-wise write enable vector  $\{A | B\}_BM$ .

Data is only written to the RAM if  $\{A | B\}_EN$ ,  $\{A | B\}_WE$  and the corresponding bitmask  $\{A | B\}_BM$  are active. Reading of data depends on the selected access mode and the values of  $\{A | B\}_WE$  and  $\{A | B\}_BM$ . The address modes are listed in Table 2.8 and 2.9. They show all combinations of  $\{A | B\}_EN$ ,  $\{A | B\}_WE$  and  $\{A | B\}_BM$  in both modes NO CHANGE and WRITE THROUGH as well as the resulting actions.

**Table 2.8:** Access combinations in NO CHANGE mode with {A|B}\_EN = 1 (SDP and TDP)

| {A B}_WE <sup>1</sup> | {A B}_BM[i] | Action on memory and {A B}_D0          |

|-----------------------|-------------|----------------------------------------|

| 0                     | 0           | Single read, no update on mem[addr][i] |

| 1                     | 0           | Last read, no update on mem[addr][i]   |

| 0                     | 1           | Single read, no update on mem[addr][i] |

| 1                     | 1           | Last read, with update on mem[addr][i] |

<sup>1</sup> Only A\_WE in SDP mode.

**Table 2.9:** Access combinations in WRITE THROUGH mode with {A|B}\_EN = 1 (TDP only)

| {A B}_WE | {A B}_BM[i] | Action on memory and {A B}_D0              |

|----------|-------------|--------------------------------------------|

| 0        | 0           | Single read, no update on mem[addr][i]     |

| 1        | 0           | Single read, no update on mem[addr][i]     |

| 0        | 1           | Single read, no update on mem[addr][i]     |

| 1        | 1           | Write through, with update on mem[addr][i] |

A single read access without any write operation occurs always if the enable signal is active  $(\{A | B\} EN = 1)$  and all write enable signals are inactive  $(\{A | B\} BM = 0, \{A | B\} WE = 0)$ . A single read access is supported in both modes SDP and TDP as shown in Figure 2.14.

All RAM cells can be initialized during configuration and used as read-only memory (ROM). To use the ROM mode the write enable has to be set to zero. The memory mapping for initialization is described in Section 2.4.6.

The NO CHANGE mode is a plain write access with active global enable ( $\{A | B\}_EN = 1$ ) and write enable signals ( $\{A | B\}_BM >= 1 \text{ or } \{A | B\}_WE = 1$ ). The output remains the last read data, i.e. after a single read, and is not affected by a write access. A NO CHANGE access is supported in both modes SDP and TDP as shown in Figure 2.15.

A read first access can be carried out in two clock cycles by first reading a word and then performing a write access in the following cycle.

#### Architecture

Figure 2.14: Timing diagram of a single read access with optional (\*) output register

Figure 2.15: Timing diagram of a NO CHANGE access with optional (\*) output register

The timing diagram 2.16 illustrates the WRITE THROUGH access, which is a simultaneous write and read access with active global enable ( $\{A | B\}_EN = 1$ ) and write enable signals ( $\{A | B\}_BM >= 1 \text{ or } \{A | B\}_WE = 1$ ). New data is written into the memory and simultaneously propagated to the outputs, also known as a transparent write. WRITE THROUGH is only supported in TDP mode.

# 2.4.9 FIFO Application

Each GateMate<sup>™</sup> block RAM cell has an integrated synchronous and asynchronous FIFO controller, allowing usage of a block RAM cell as FIFO memory in the 40K configurations only.

Port B is the write / push port of the FIFO and port A is the read / pop port. In case of syn-

Architecture

Figure 2.16: Timing diagram of a WRITE THROUGH access with optional (\*) output register

chronous FIFO, A\_CLK is used as clock for both write / push and read / pop.

Since the FIFO mode is an extension to the TDP/SDP 40K mode, it supports the same bitwidth configurations as shown in Tables 2.5 (page 32) and 2.7. Widths of the input and output buses must be equal.

- TDP 40K, with arbitrary but equal input and output bit width

- SDP 40K, with fixed 80 bit input and output bit width

Figure 2.17: Internal data flow of DPSRAM in FIFO mode

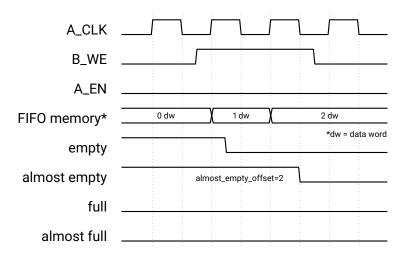

In FIFO configuration, the incoming address signals are ignored. Instead, internal read and write pointers with correct alignment according to bitwidth are forwarded to the SRAM macros. Furthermore, there exist additional output signals which are solely used for FIFO monitoring and are described in Table 2.10. The F\_ALMOST\_FULL\_FLAG and F\_ALMOST\_EMPTY\_FLAG give an early warning when the FIFO is approaching its limits. Its offset can be configured using a 13 bit register during configuration or it is set dynamically using the inputs F\_ALMOST\_FULL\_OFFSET and F\_ALMOST\_EMPTY\_OFFSET.

Moreover, the FIFO controller has a dedicated active low reset input signal F\_RST\_N which is synchronized into clock domain internally.

| Flag            | Width | Description                                                                                            |

|-----------------|-------|--------------------------------------------------------------------------------------------------------|

| F_FULL          | 1     | All entries in the FIFO are filled, is set on the rising edge of the write clock (asynchronous)        |

| F_EMPTY         | 1     | The FIFO is empty, is set on the rising edge of the read clock (asyn-<br>chronous)                     |

| F_ALMOST_FULL   | 1     | Almost all entries in the FIFO are filled, is set on the rising edge of the write clock (asynchronous) |

| F_ALMOST_EMPTY  | 1     | Almost all entries in FIFO have been read, is set on the rising edge of the read clock (asynchronous)  |

| F_READ_ADDRESS  | 16    | Current FIFO read pointer                                                                              |

| F_WRITE_ADDRESS | 16    | Current FIFO write pointer                                                                             |

| F_RD_ERR        | 1     | Is set if FIFO is empty and a read access takes place                                                  |

| F_WR_ERR        | 1     | Is set if FIFO is full and data is pushed, new data will be lost                                       |

| Table 2.10: FIFO status flags |

|-------------------------------|

|-------------------------------|

Table 2.11 illustrates the valid FIFO data concatenations for the variable bitwidth data TDP mode. B\_EN and B\_WE are the write / push enable and A\_EN is the read / pop enable signal.

Table 2.11: FIFO 40 bit data concatenations

| Function     | Width | Concatenation |

|--------------|-------|---------------|

| Push data    | 40    | B_DI[39:0]    |

| Push bitmask | 40    | B_BM[39:0]    |

| Pop data     | 40    | A_DO[39:0]    |

Table 2.12 illustrates the valid FIFO data concatenations for the 80 bit data SDP mode. B\_EN and B\_WE are the write / push enable and A\_EN is the read / pop enable signal.

| Function     | Width | Concatenation           |

|--------------|-------|-------------------------|

| Push data    | 80    | B_DI[39:0]∘A_DI[39:0]   |

| Push bitmask | 80    | B_BM[39:0]∘A_BM[39:0]   |

| Pop data     | 80    | B_D0[39:0] • A_D0[39:0] |

| 1            |       |                         |

Table 2.12: FIFO 80 bit data concatenations

<sup>1</sup> Symbol  $\circ$  is concatenation.

#### Synchronous FIFO Access

Write / push and read / pop pointers are both registered with the rising clock edge of A\_CLK. During the write / push operation, the data word available at  $\{A, B\}_DI / \{A, B\}_BM$  is written into the FIFO whenever the B\_EN and B\_WE signals are active one setup time before the rising clock edge of A\_CLK. The write / push operation presents the data word at  $\{A0, A1\}_D0$  whenever the A\_EN signal is active one setup time the rising clock edge of A\_CLK.

The signals empty, full, almost empty, almost full, read and write error are combinatorial computed out of read and write pointer. The error flags are not sticky.

The timing diagram in Figure 2.18 illustrates the writing to an empty synchronous FIFO.

Figure 2.18: Writing to an empty synchronous FIFO

The timing diagram in Figure 2.19 illustrates the writing to an almost full synchronous FIFO.

The timing diagram in Figure 2.20 illustrates the reading from a full synchronous FIFO.

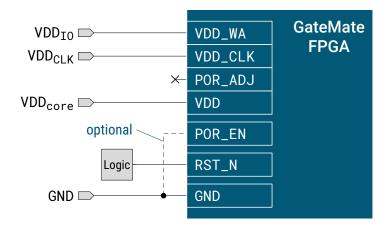

Figure 2.20: Reading from a full synchronous FIFO